# Project Report ATC-133

# TCAS Experimental Unit (TEU) Hardware Description

D.A. Spencer R.R. LaFrey J. DiBartolo W.H. Harman

6 June 1986

# **Lincoln Laboratory**

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Lexington, Massachusetts

Prepared for the Federal Aviation Administration, Washington, D.C. 20591.

This document is available to the public through the National Technical Information Service, Springfield, VA 22161 This document is disseminated under the sponsorship of the Department of Transportation in the interest of information exchange. The United States Government assumes no liability for its contents or use thereof.

| 1. Report No.                                                         | 2. Government Accession No.     | 3. Recipient's Catalog No.            |

|-----------------------------------------------------------------------|---------------------------------|---------------------------------------|

| DOT/FAA/PM-85/2                                                       |                                 |                                       |

| 4. Title and Subtitle                                                 | •                               | 5. Report Date<br>6 June 1986         |

| TCAS Experimental Unit (TEU) Har                                      | 6. Performing Organization Code |                                       |

| 7. Author(s)                                                          |                                 | 8. Performing Organization Report No. |

| David A. Spencer Joseph DiBartolo Raymond R. LaFrey William H. Harman |                                 | ATC-133                               |

| 3. Performing Organization Name and Address                           |                                 | 10. Work Unit No. (TRAIS)             |

| Lincoln Laboratory, MIT                                               |                                 |                                       |

| P.O. Box 73                                                           |                                 | 11. Contract or Grant No.             |

| Lexington, MA 02173-0073                                              |                                 | DOT-FA77WAI-817                       |

|                                                                       |                                 | 13. Type of Report and Period Covered |

| 12. Sponsoring Agency Name and Address                                |                                 |                                       |

| Department of Transportation                                          |                                 | Project Report                        |

| Federal Aviation Administration                                       |                                 |                                       |

| Program Engineering and Maintenance Service                           |                                 | 14. Sponsoring Agency Code            |

| Washington, DC 20591                                                  |                                 | spencering riganes data               |

|                                                                       |                                 |                                       |

#### 15. Supplementary Notes

The work reported in this document was performed at Lincoln Laboratory, a center for research operated by Massachusetts Institute of Technology, under Air Force Contract F19628-85-C-0002.

#### 16. Abstract

This report describes the hardware design of the TCAS Experimental Units (TEU's) constructed by Lincoln Laboratory to support the design and validation of the Traffic Alert and Collision Avoidance System (TCAS) for the FAA. Section 1.0 presents an overview of the operation of the TEU's, in order to give some context for the hardware design. References are given to more extensive descriptions of the TCAS system operation and software design. Section 2.0 constitutes the bulk of the report, and is a detailed description of the TEU hardware design.

The purpose of this description is to document the design details of the equipment which was used to develop and validate the signal processing techniques and algorithms which appear in the TCAS II Minimum Operational Performance Standard, the TCAS National Standard and various technical reports listed in the references. A second purpose is to provide design guidance to potential TCAS II manufacturers, in the form of a detailed description of a feasible design with documented performance. Finally, this document is a manual for future use and maintenance of the TEU's.

| 17. Key Words  Traffic Alert and Collision threat logic Avoidance System (TCAS) fruit collision avoidance synchronous garble |                                                                          | 18. Distribution Statement  Document is available to the public through |                  | •         |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|-----------|

| Mode S whisper-shout degarble angle of arrival                                                                               | dynamic minimum threshold<br>squitter<br>TCAS Experimental<br>Unit (TEU) | the National Techni<br>Springfield, VA 221                              |                  | ervice,   |

| 19. Security Classif. (of this report)                                                                                       | 20. Security Classif. (d                                                 | f this page)                                                            | 21. No. of Pages | 22. Price |

| Unclassified                                                                                                                 | Unclassifie                                                              | d                                                                       | 130              |           |

#### OVERVIEW

This report describes the hardware design of the TCAS Experimental Units (TEU's) constructed by Lincoln Laboratory to support the design and validation of the Traffic Alert and Collision Avoidance System (TCAS) for the FAA. Section 1.0 presents an overview of the operation of the TEU's, in order to give some context for the hardware design. References are given to more extensive descriptions of the TCAS system operation and software design. Section 2.0 constitutes the bulk of the report, and is a detailed description of the TEU hardware design.

The purpose of this description is to document the design details of the equipment which was used to develop and validate the signal processing techniques and algorithms which appear in the TCAS II Minimum Operational Performance Standard [Ref. 6], the TCAS National Standard [Ref. 8] and various technical reports listed in the references. A second purpose is to provide design guidance to potential TCAS II manufacturers, in the form of a detailed description of a feasible design with documented performance. Finally, this document is a manual for future use and maintenance of the TEU's.

## CONTENTS

|     | Overv<br>Illus<br>Table | strations                                                               | iii<br>vi<br>viii |

|-----|-------------------------|-------------------------------------------------------------------------|-------------------|

| 1.0 | 1.1                     | ODUCTION<br>Purpose                                                     | 1<br>1            |

|     | 1.2                     | Summary of Operation                                                    | 1                 |

| 2.0 | TCAS                    | EQUIPMENT                                                               | 4                 |

|     |                         | Major System Elements                                                   | 4                 |

|     |                         | Modulation Control Unit                                                 |                   |

|     |                         | 2.2.1 Function                                                          | 8                 |

|     |                         | 2.2.2 Programming                                                       | 8<br>8<br>9<br>9  |

|     |                         | 2.2.3 Operation                                                         | 9                 |

|     |                         | 2.2.3.1 Summary                                                         | 1.2               |

|     |                         | 2.2.3.2 MCU Controller 2.2.3.3 Mode Decoder and Sequence Generator      | 13                |

|     |                         | 2.2.3.4 Mode S Data Buffer and DPSK Generator                           | 17                |

|     |                         | 2.2.3.5 Range Counter                                                   | 20                |

|     |                         | 2.2.3.6 Suppression Logic                                               | 22                |

|     | 2.3                     | Transmitter/Receiver                                                    | 24                |

|     |                         | 2.3.1 Microwave Signal Source (1030 MHz)                                | 24                |

|     |                         | 2.3.2 Transmitter Chain                                                 | 24                |

|     |                         | 2.3.2.1 PAM/DPSK Modulators                                             | 27                |

|     |                         | 2.3.2.2 Microwave Power Module                                          | 27<br>29          |

|     |                         | 2.3.2.3 Digital Attenuator 2.3.2.4 Bandpass Filter                      | 29                |

|     |                         | 2.3.3 Antenna Interface and Transmitter Monitor                         | 29                |

|     |                         | 2.3.4 Receiver Chain                                                    | 29                |

|     | 2.4                     | Video Pulse Quantizer                                                   | 32                |

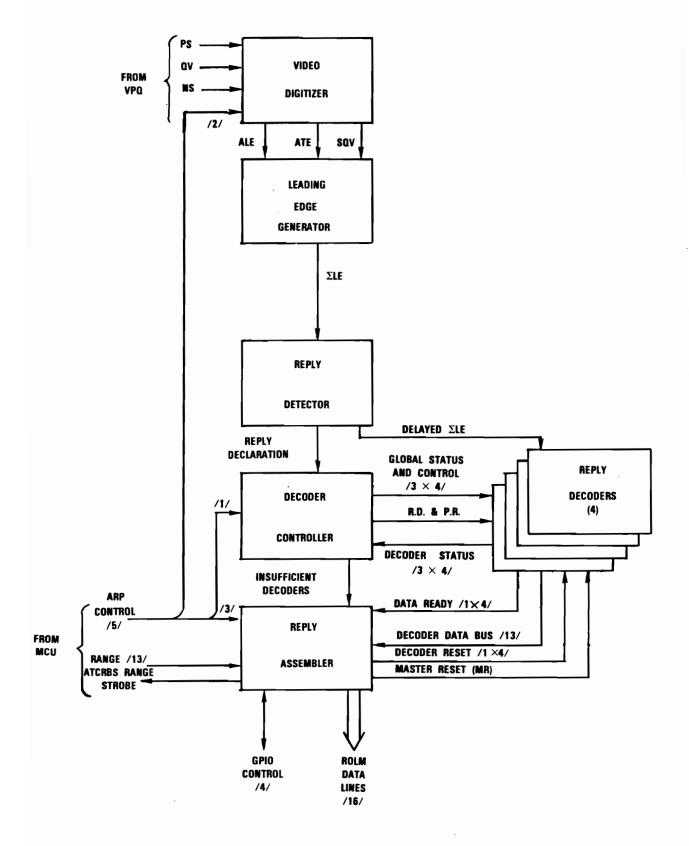

|     | 2.5                     | Video Digitizer and ATCRBS Reply Processor                              | 39                |

|     |                         | 2.5.1 General Description                                               | 39                |

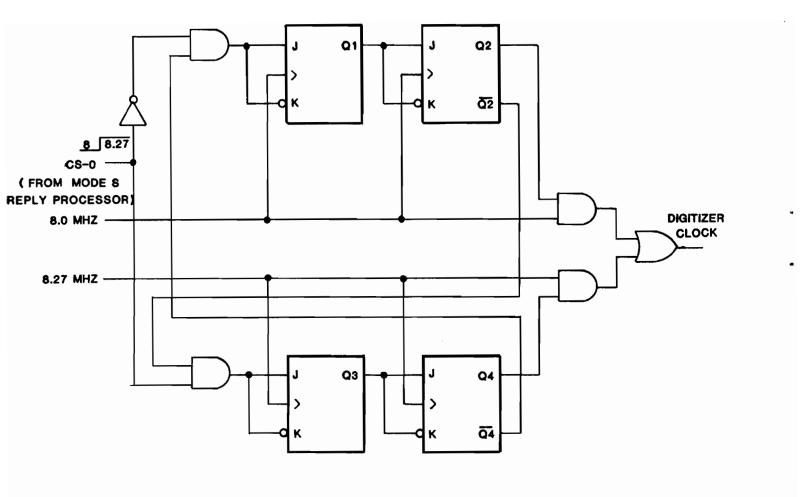

|     |                         | 2.5.2 Video Digitizer                                                   | 4.5               |

|     |                         | 2.5.3 Pseudo Leading Edge Generation and Short Pulse                    | 1. 1              |

|     |                         | Rejection 2.5.4 Reply Detection                                         | 45<br>53          |

|     |                         | 2.5.5 Reply Decoder Processing                                          | 53                |

|     |                         | 2.5.6 Reply Assembler                                                   | 58                |

|     | 2.6                     | Mode S Reply Processor                                                  | 62                |

|     |                         | 2.6.1 General Description                                               | 62                |

|     |                         | 2.6.2 State Controller                                                  | 64                |

|     |                         | 2.6.3 Sliding Window Detector                                           | 68                |

|     |                         | 2.6.4 Preamble Detector                                                 | 68                |

|     |                         | 2.6.5 Message Processor                                                 | 68                |

|     |                         | 2.6.6 Computer Interface Controller                                     | 77                |

|     |                         | 2.6.6.1 Discrete or Squitter Reply Transfer 2.6.6.2 Test Reply Transfer | 77<br>77          |

|     |                         | ICOC NCDLY ILANDICI                                                     | //                |

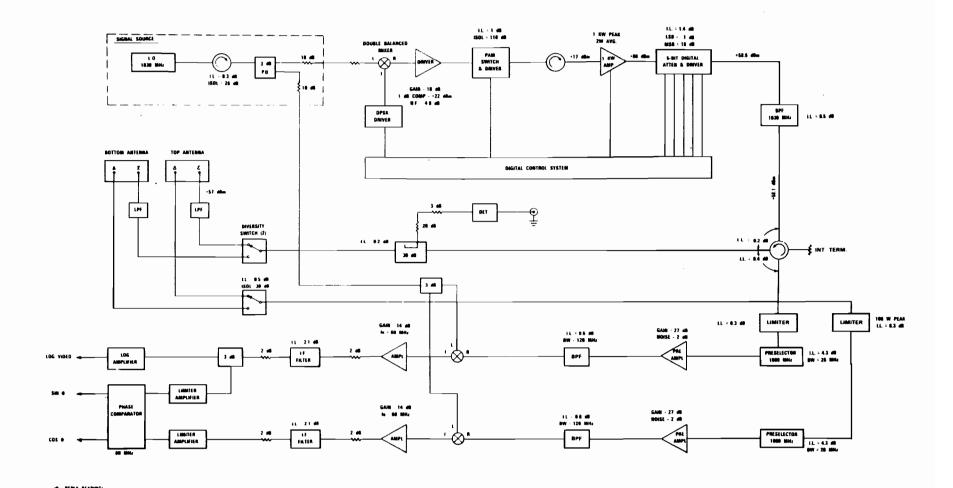

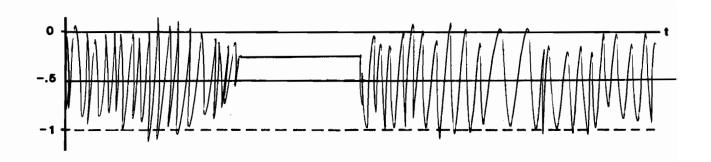

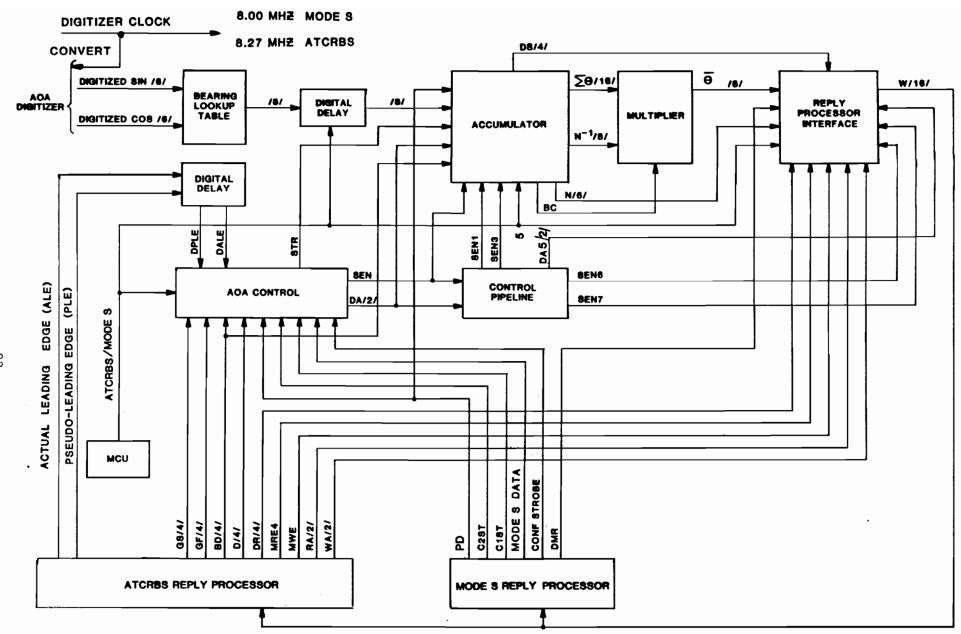

| 2.7       | Angle of Arrival (AOA) Subsystem                    | 77    |

|-----------|-----------------------------------------------------|-------|

|           | 2.7.1 Antenna and Antenna Feed Network              | 83    |

|           | 2.7.2 AOA Receiver                                  | 83    |

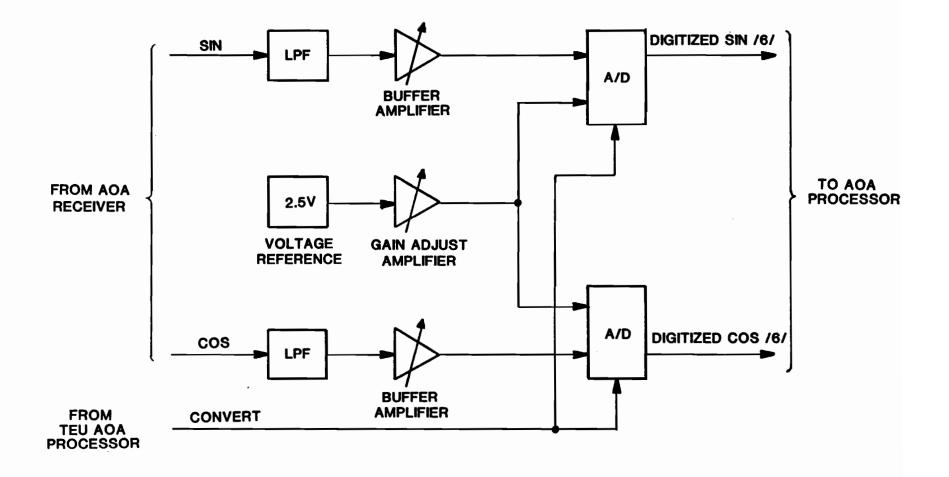

|           | 2.7.3 AOA Digitizer                                 | 89    |

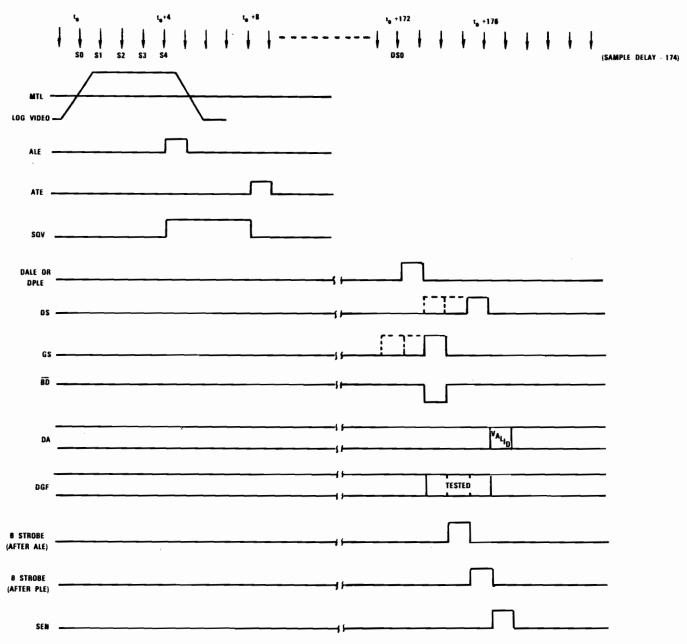

|           | 2.7.4 AOA Processor                                 | 89    |

|           | 2.7.4.1 AOA Control                                 | 93    |

|           | 2.7.4.1.1 AOA ATCRBS Control                        | 93    |

|           | 2.7.4.1.2 AOA Mode S Controller                     | 99    |

|           | 2.7.4.2 AOA Accumulator                             | 99    |

|           | 2.7.4.3 AOA Reply Processor Interface               | 101   |

| 2.8       | Mode S Transponder Interface                        | 104   |

|           | 2.8.1 Purpose                                       | 104   |

|           | 2.8.2 TEU Implementation                            | 108   |

|           | 2.8.3 General Principles                            | 108   |

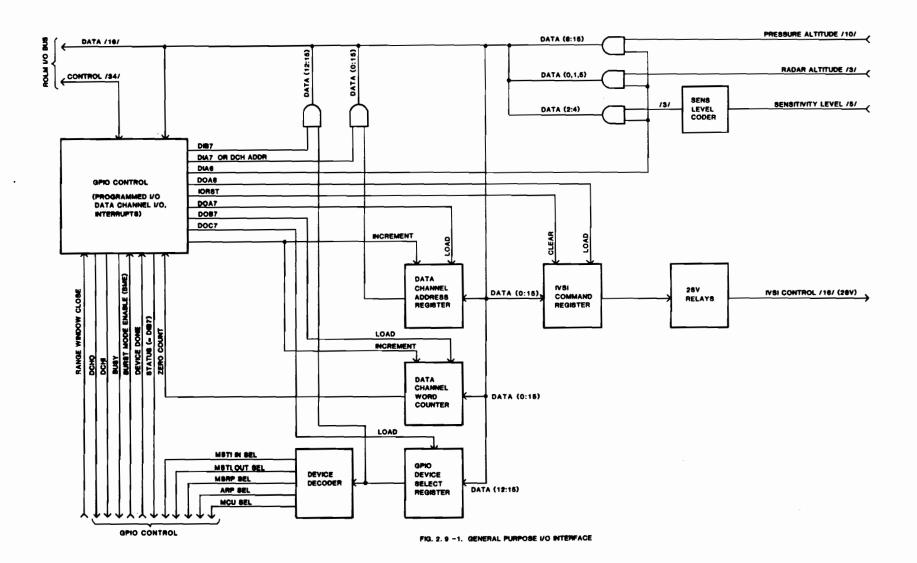

| 2.9       | General Purpose I/O Interface                       | 108   |

|           | 2.9.1 Function                                      | 108   |

|           | 2.9.2 Summary of I/O Interface Conventions          | 109   |

|           | 2.9.3 Programming the General Purpose I/O Interface | e 111 |

|           | 2.9.4 Operation                                     | 116   |

| 2.10      | Real-Time Clock                                     | 118   |

|           | 2.10.1 General Description                          | 118   |

|           | 2.10.2 Programming                                  | 119   |

| 2.11      | Bootstrap Loading                                   | 119   |

| REFERENCE | ES                                                  | 121   |

# ILLUSTRATIONS

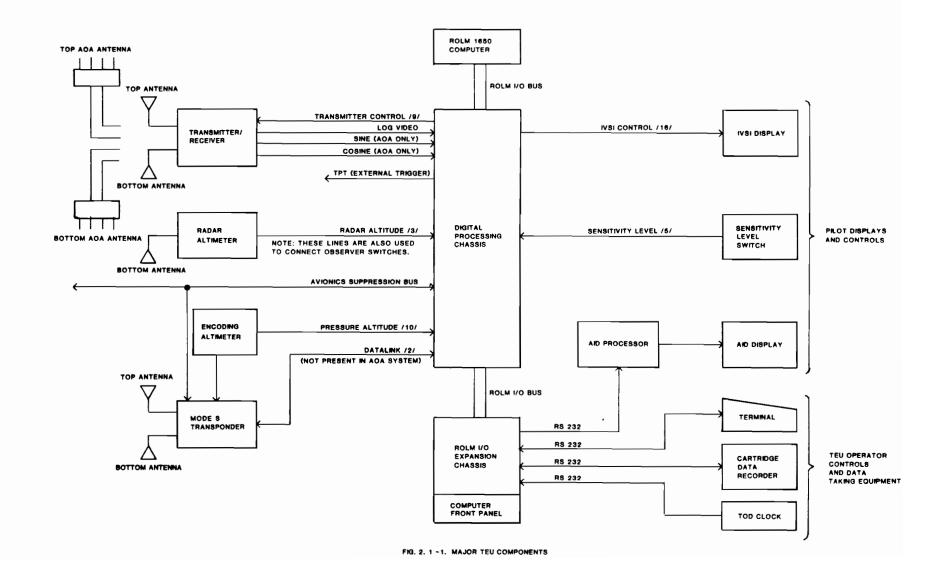

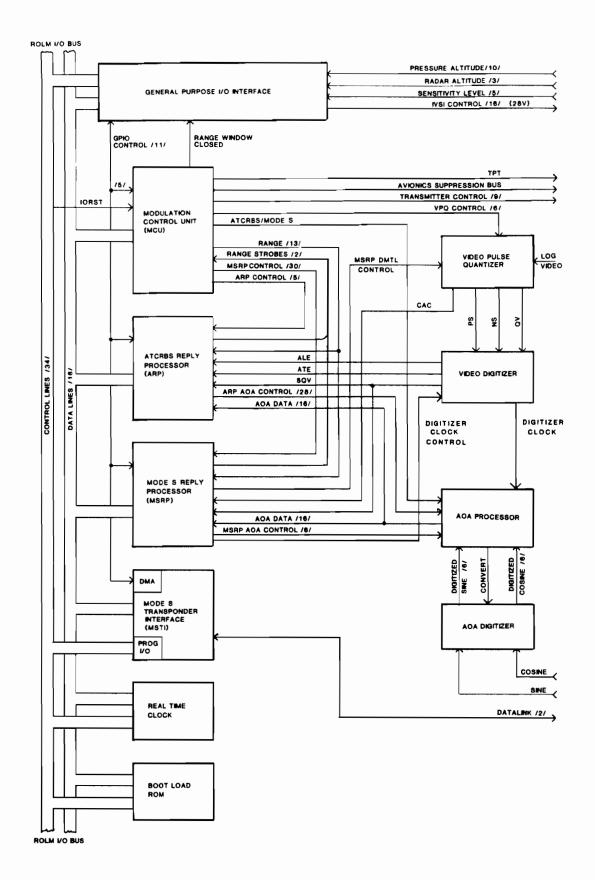

| 2 · 1 - 1<br>2 · 1 - 2 | Major TEU components<br>Digital processing chassis components and interconnections | 5<br>6 |

|------------------------|------------------------------------------------------------------------------------|--------|

| 2.2-1                  | MCU control block format                                                           | 10     |

| 2.2-2                  | MCU block diagram                                                                  | 12     |

| 2.2-3                  | MCU controller block diagram                                                       | 14     |

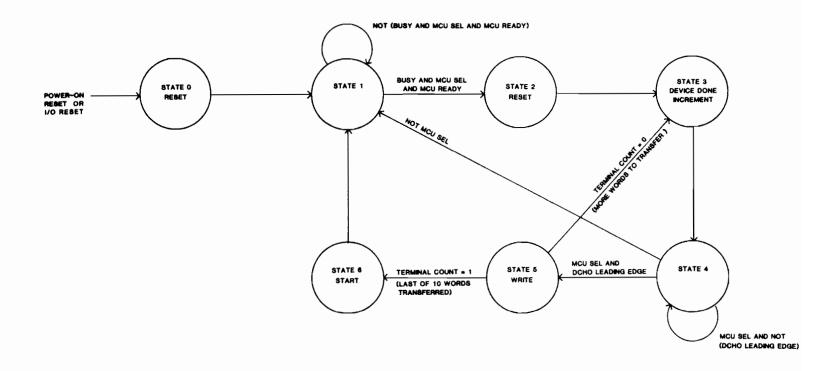

| 2.2-4                  | MCU controller state diagram                                                       | 15     |

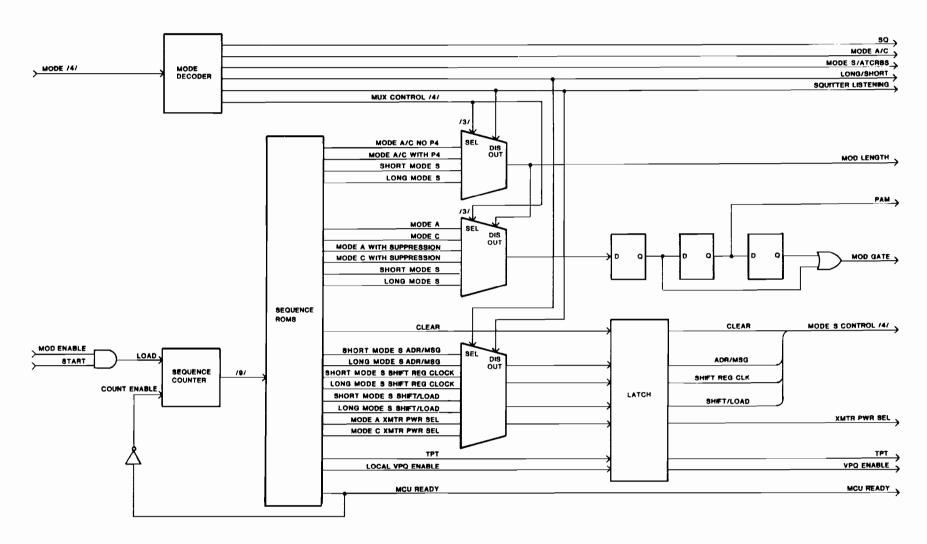

| 2.2-5                  | MCU mode decoder and sequence generator                                            | 16     |

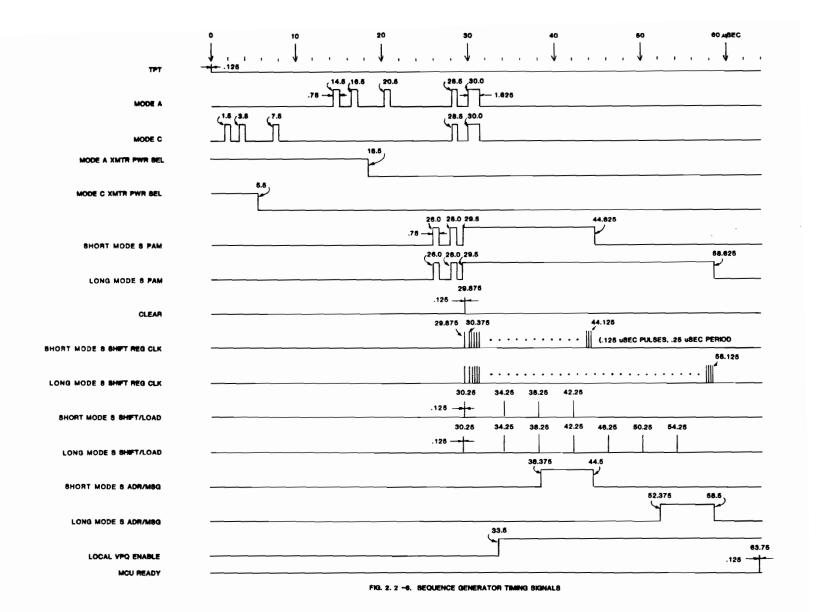

| 2.2-6                  | Sequence generator timing signals                                                  | 18     |

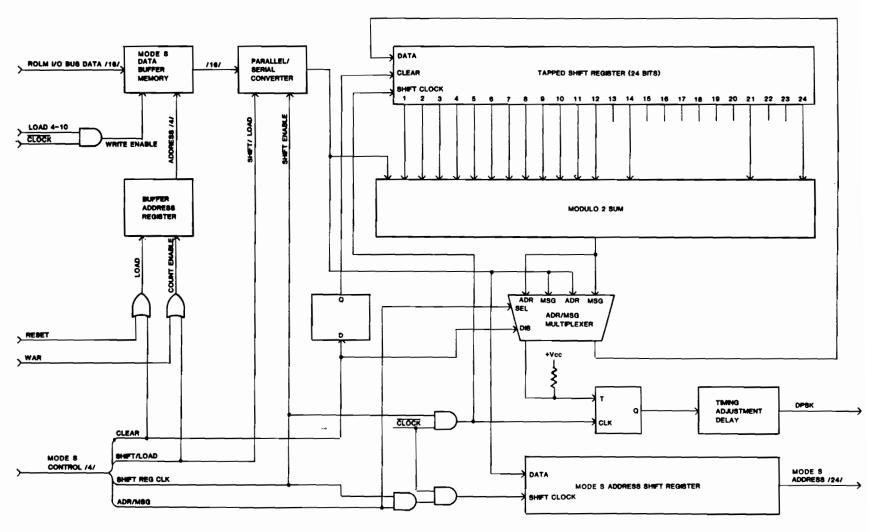

| 2.2-7                  | Mode S data buffer and DPSK generator                                              | 19     |

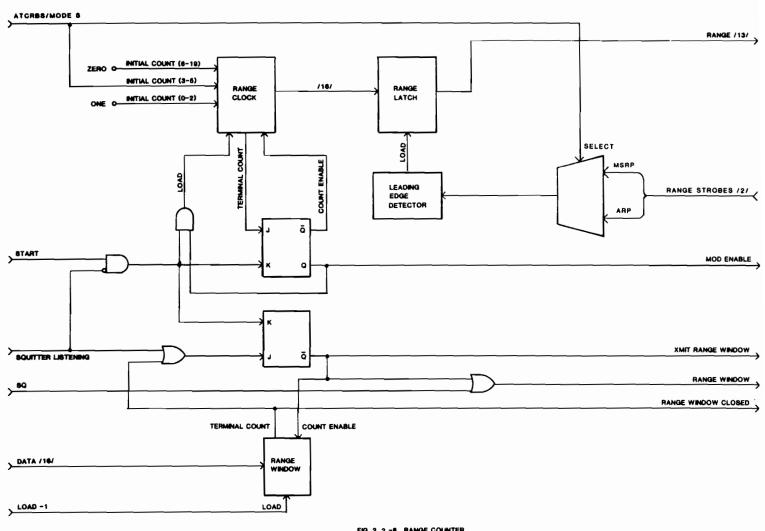

| 2.2-8                  | Range counter                                                                      | 21     |

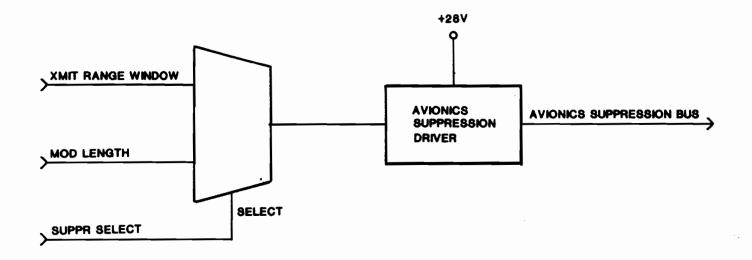

| 2.2-9                  | Suppression logic                                                                  | 23     |

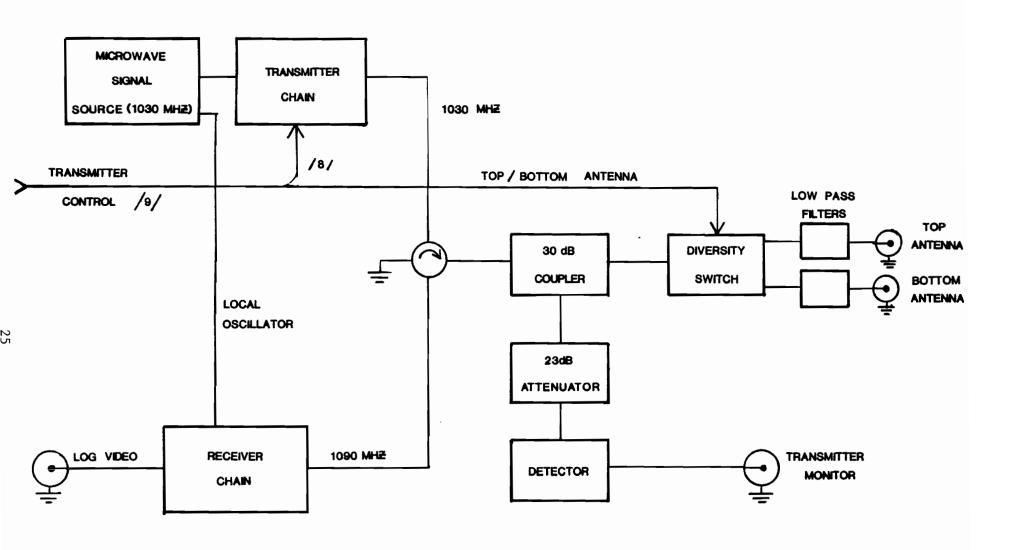

| 2.3-1                  | TEU transmitter/receiver block diagram                                             | 25     |

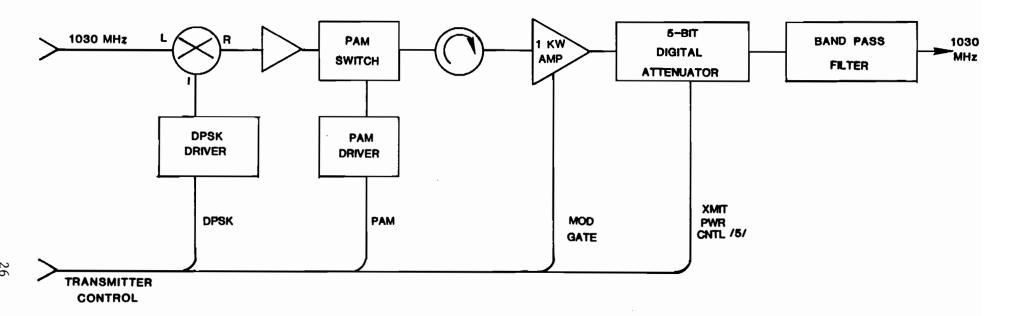

| 2.3-2                  | Transmitter chain block diagram                                                    | 26     |

| 2.3-3                  | Power module response to DPSK transition                                           | 28     |

| 2.3-4                  | Transmitter power supply interlock circuit                                         | 30     |

| 2.3-5                  | Receiver chain block diagram                                                       | 31     |

| 2.3-6                  | Receiver log video response                                                        | 34     |

| 2.4-1                  | VPQ simplified circuit diagram                                                     | 36     |

| 2.4-2                  | VPQ waveforms                                                                      | 37     |

| 2.4-3                  | VPQ DMTL timing network                                                            | 38     |

| 2.4-4                  | ATCRBS DMTL waveforms                                                              | 40     |

| 2.4-5                  | Mode S DMTL waveforms                                                              | 40     |

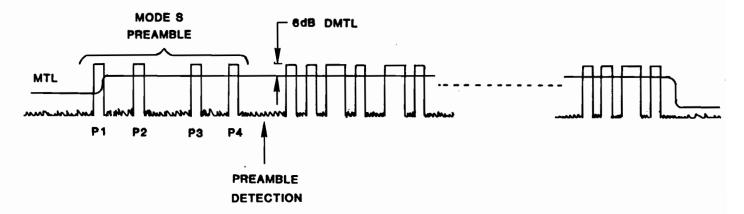

| 2.5-1                  | ATCRBS reply processor block diagram                                               | 41     |

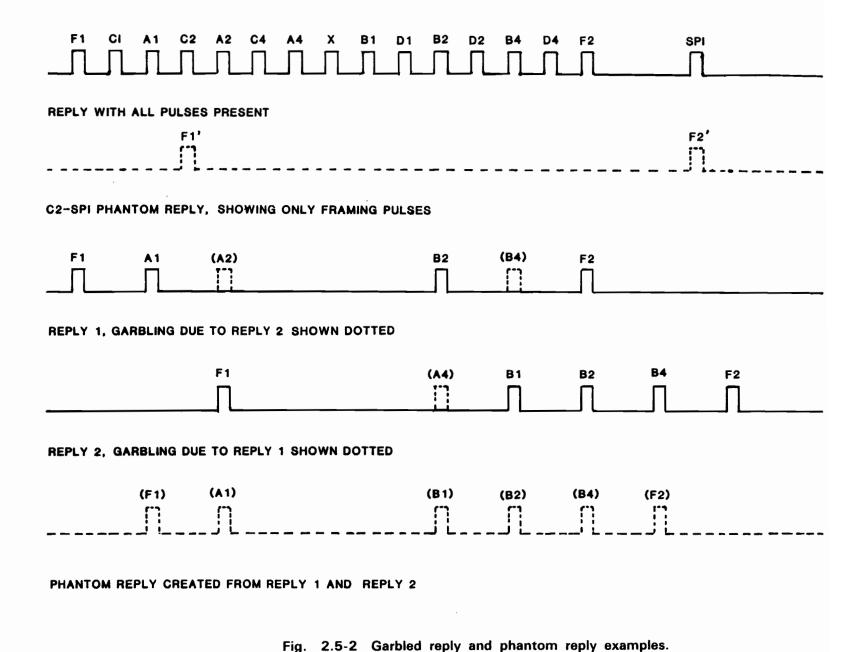

| 2.5-2                  | Garbled reply and phantom reply examples                                           | 43     |

| 2.5-3                  | ATCRBS reply processor data format                                                 | 44     |

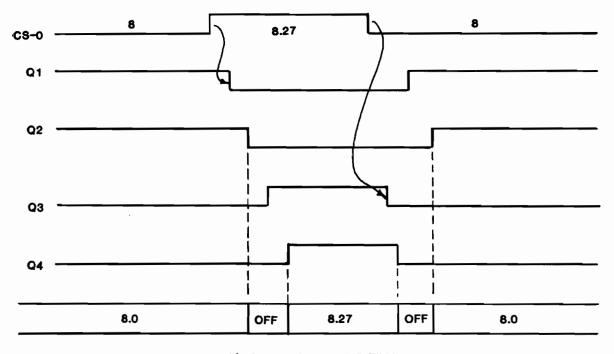

| 2.5-4                  | Digitizer clock control                                                            | 46     |

| 2.5-5                  | Digitizer logic                                                                    | 47     |

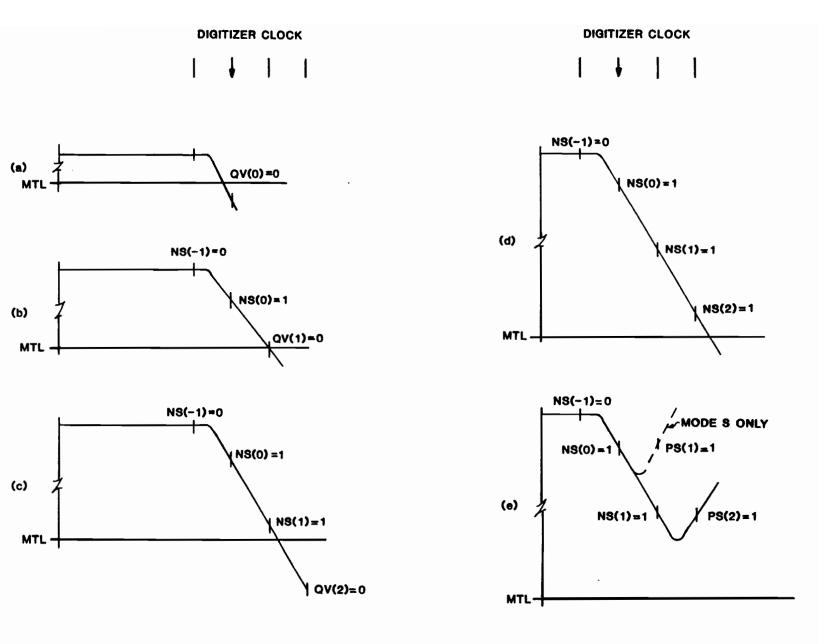

| 2.5-6                  | Trailing edge conditions                                                           | 48     |

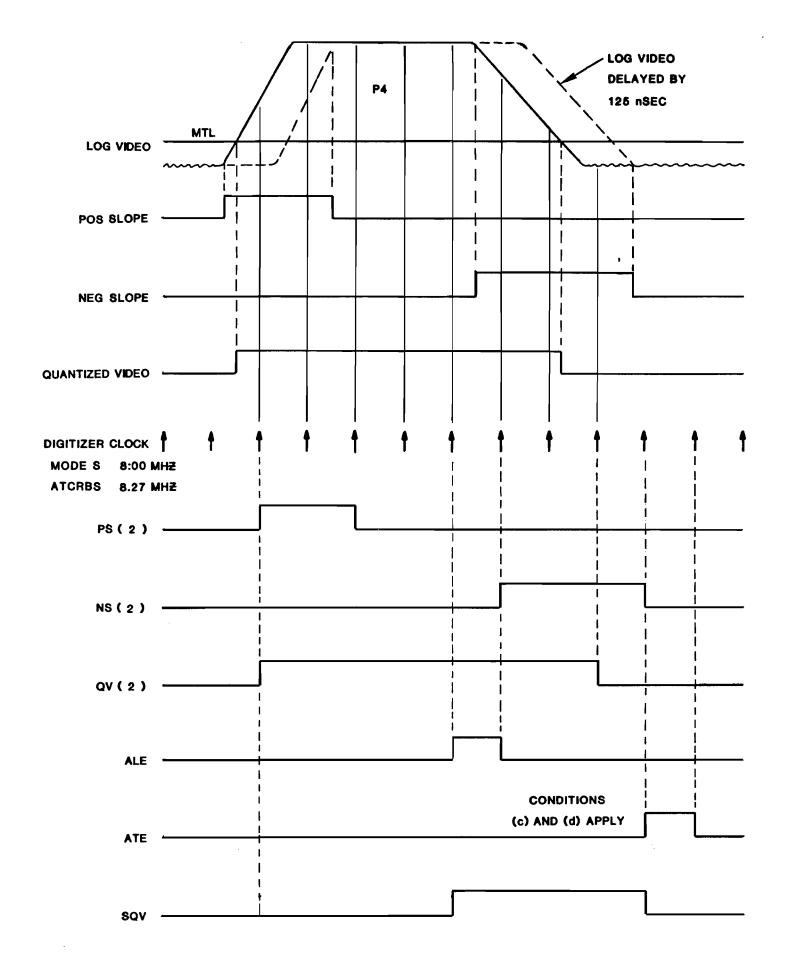

| 2.5-7                  | Digitizer timing                                                                   | 49     |

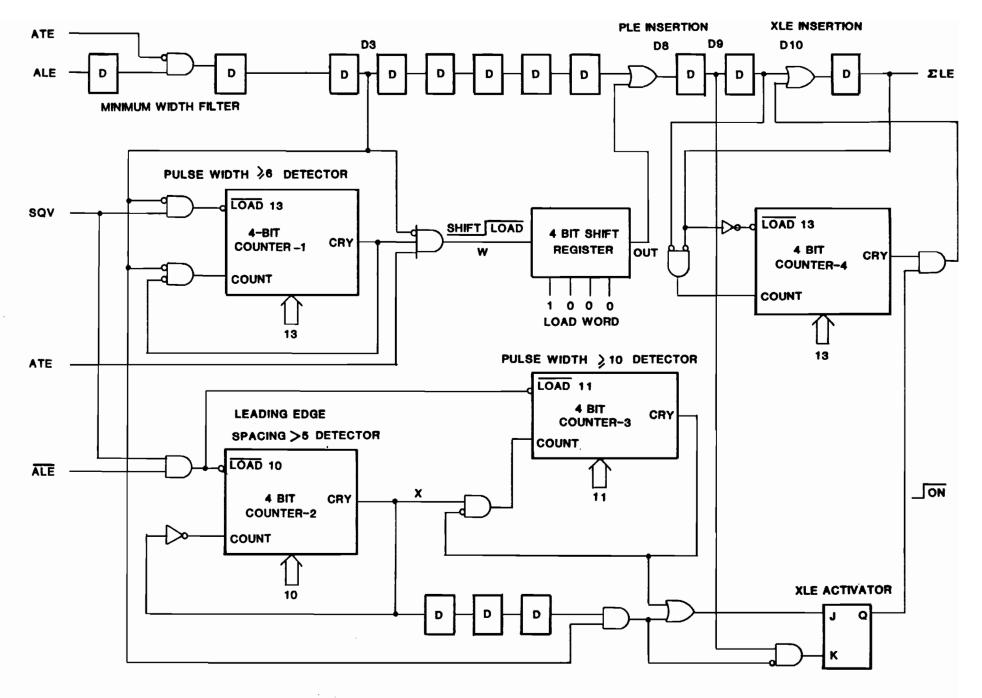

| 2.5-8                  | Pseudo and extra leading edge generator                                            | 50     |

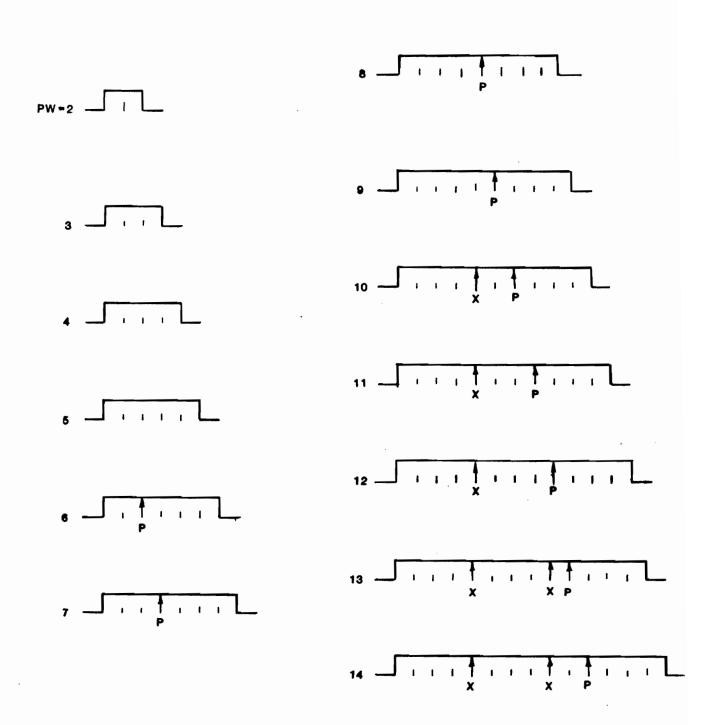

| 2.5-9                  | Pseudo and extra leading edge pulse generation, no embedded ALE's                  | 51     |

| 2.5-10                 | Extra leading edge generation with embedded ALE's                                  | 52     |

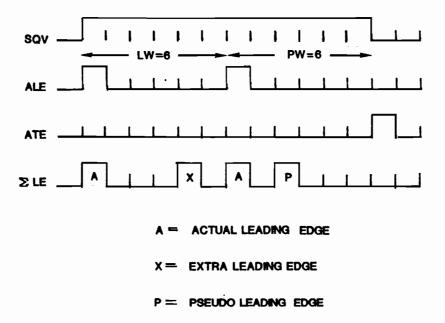

| 2.5-11                 | Reply detector                                                                     | 54     |

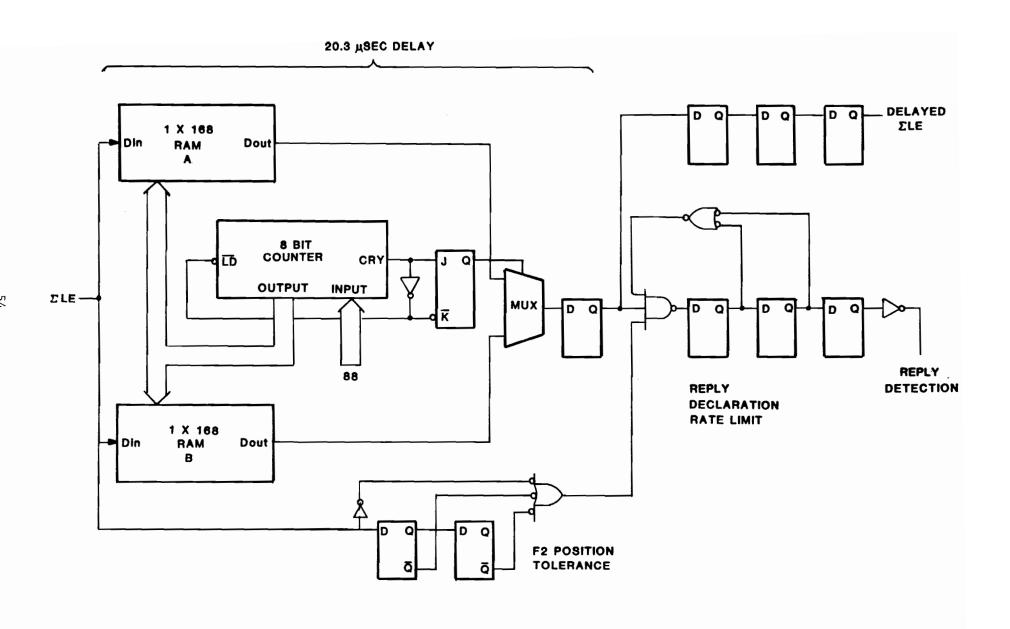

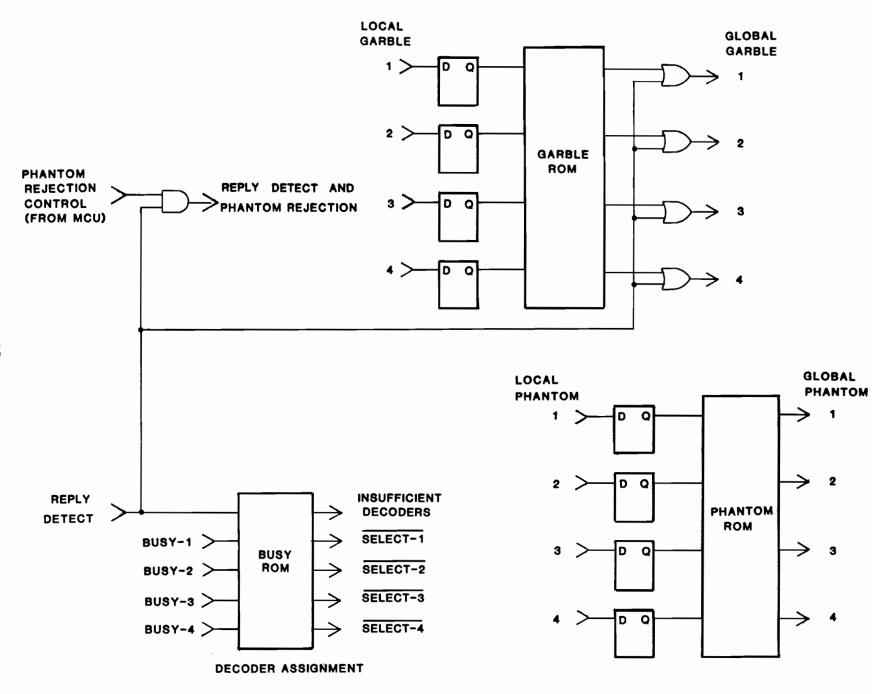

| 2.5-12                 | Reply decoder control                                                              | 55     |

| 2.5-13                 | Reply decoder number 1                                                             | 56     |

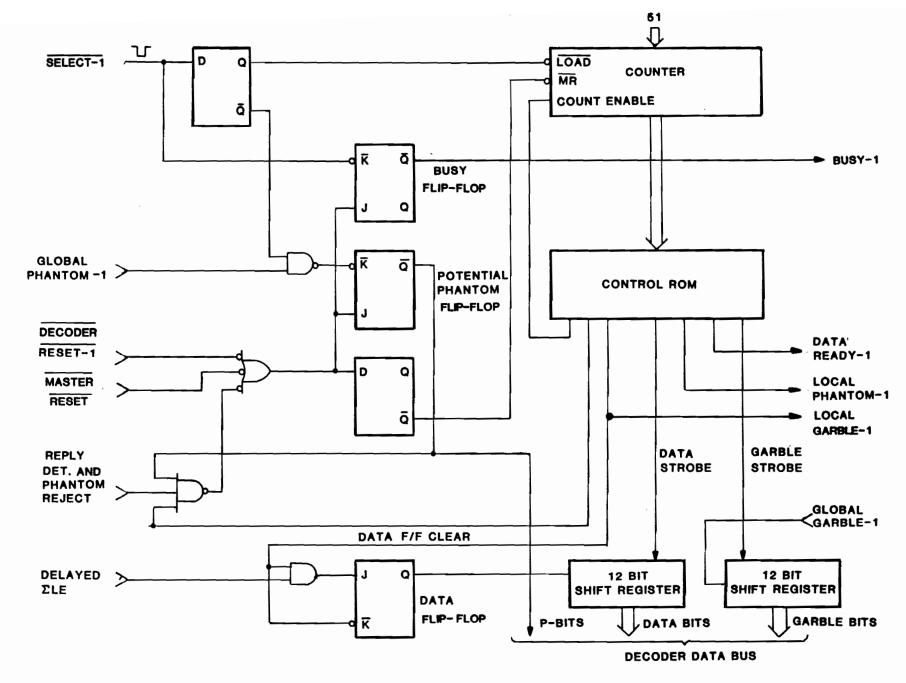

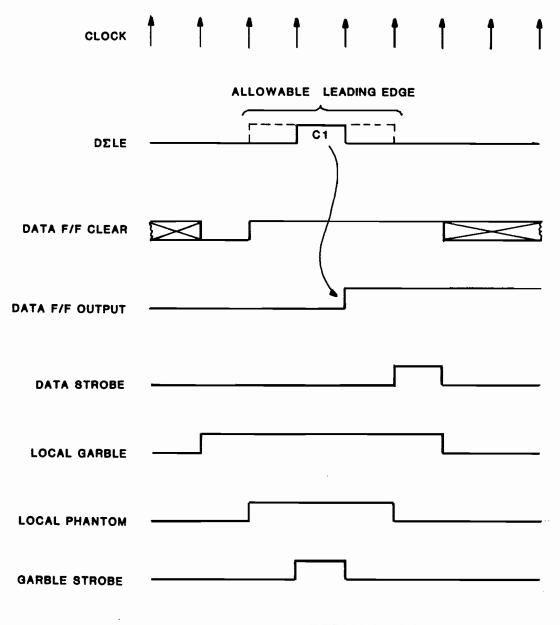

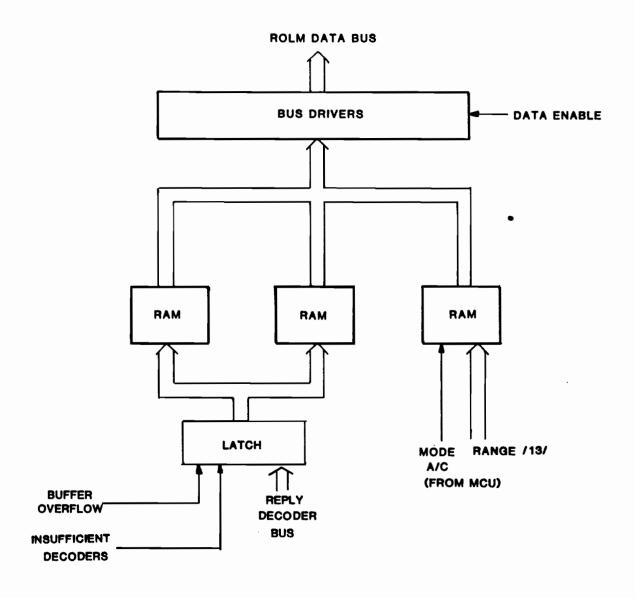

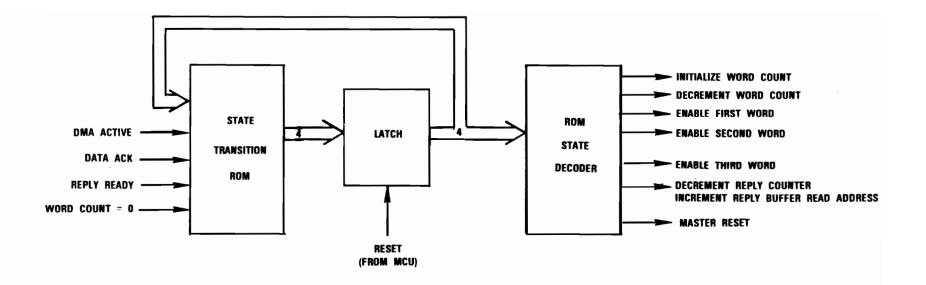

| 2.5-14                 | Reply decoder timing                                                               | 57     |

| 2.5-15                 | Reply data output logic                                                            | 59     |

| 2.5-16                 | Reply assembler state controller and associated circuitry                          | 60     |

| 2.5-17                 | State diagram of reply assembler controller                                        | 61     |

| 2.6-1            | Mode S reply processor block diagram                           | 63  |

|------------------|----------------------------------------------------------------|-----|

| 2.6-2            | Mode S reply processor data formats                            | 65  |

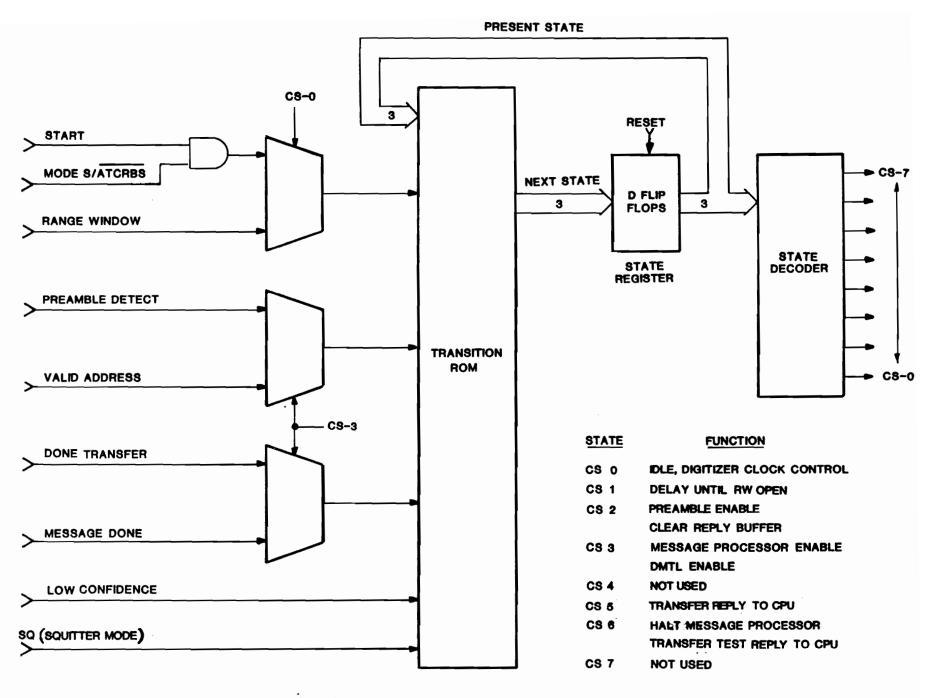

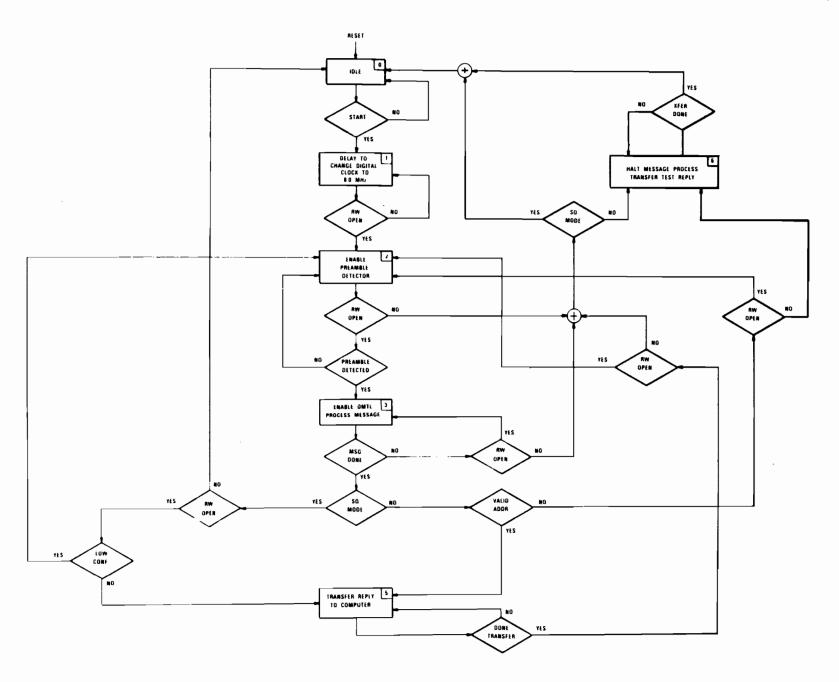

| 2.6-3            | State controller block diagram                                 | 66  |

| 2.6-4            | State controller state diagram                                 | 67  |

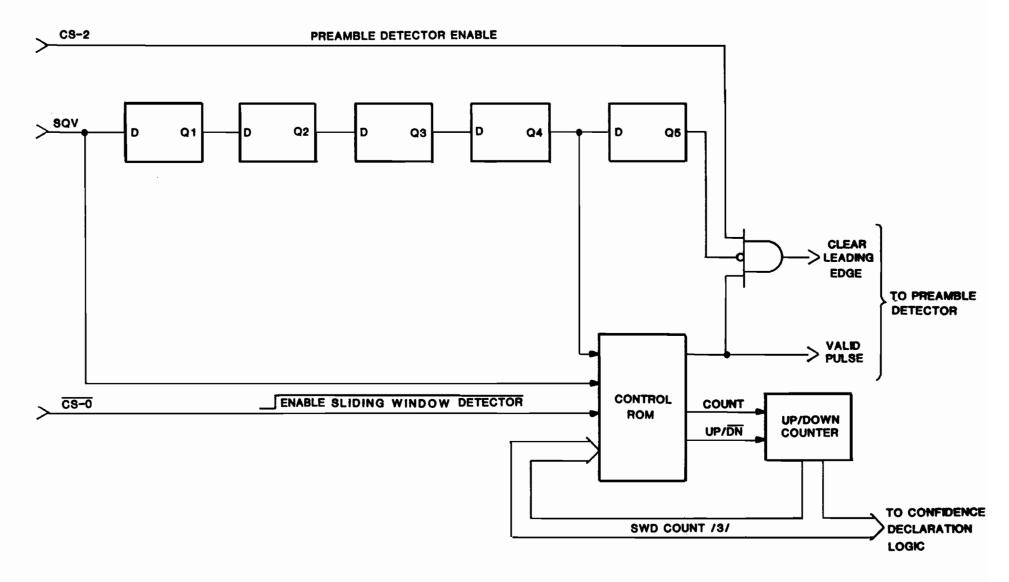

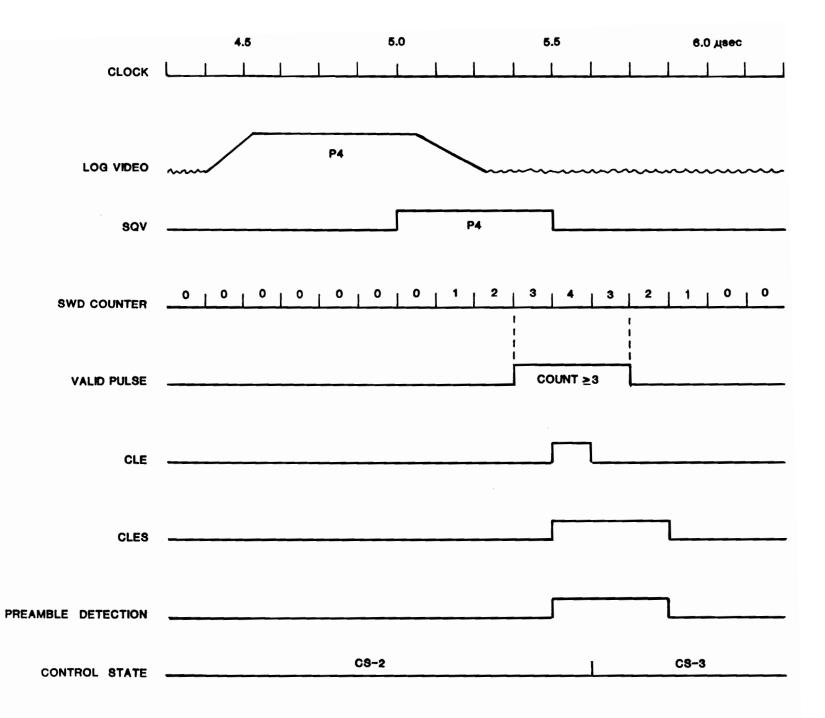

| 2.6-5            | Sliding window detector                                        | 69  |

| 2.6-6            | Mode S preamble detection timing                               | 70  |

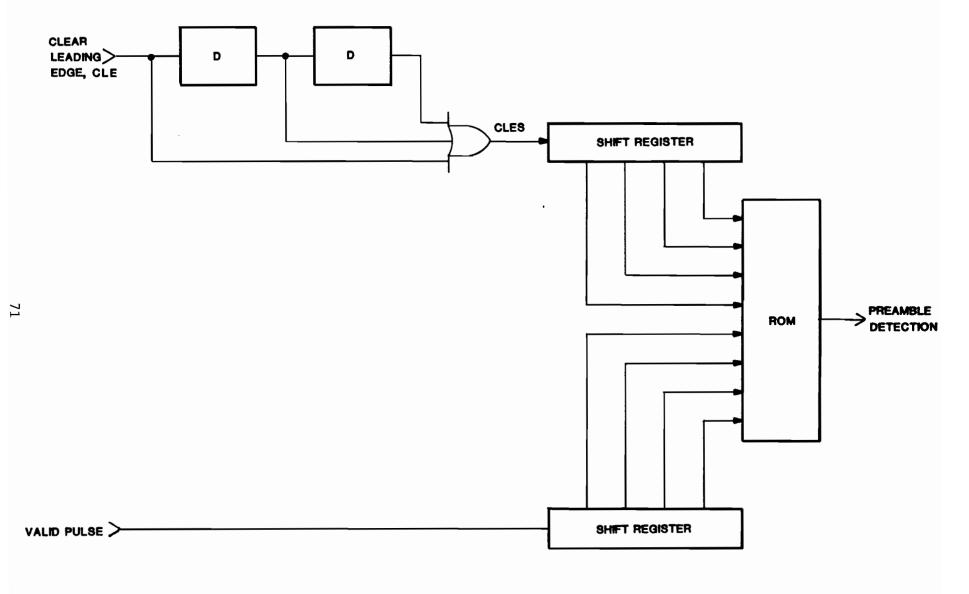

| 2.6-7            | Preamble detector                                              | 7   |

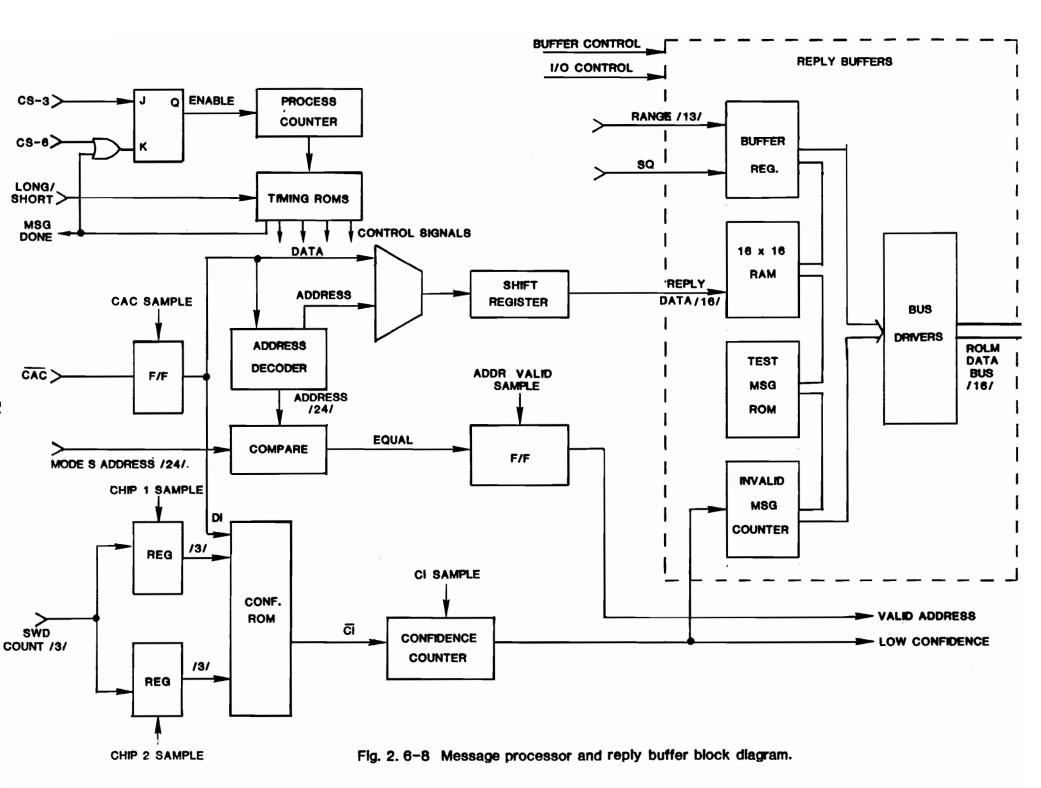

| 2.6-8            | Message processor and reply buffer block diagram               | 72  |

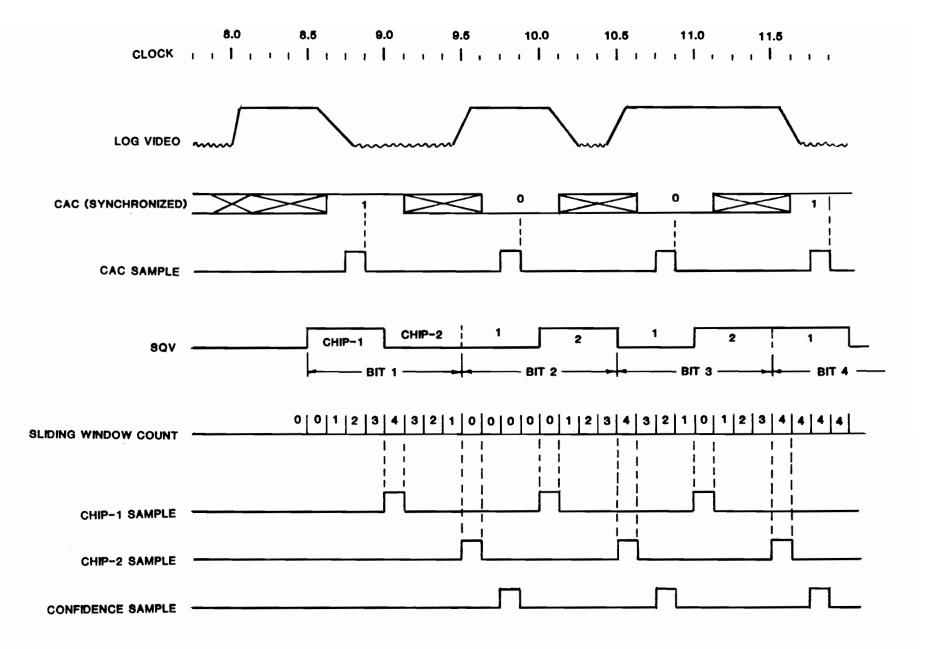

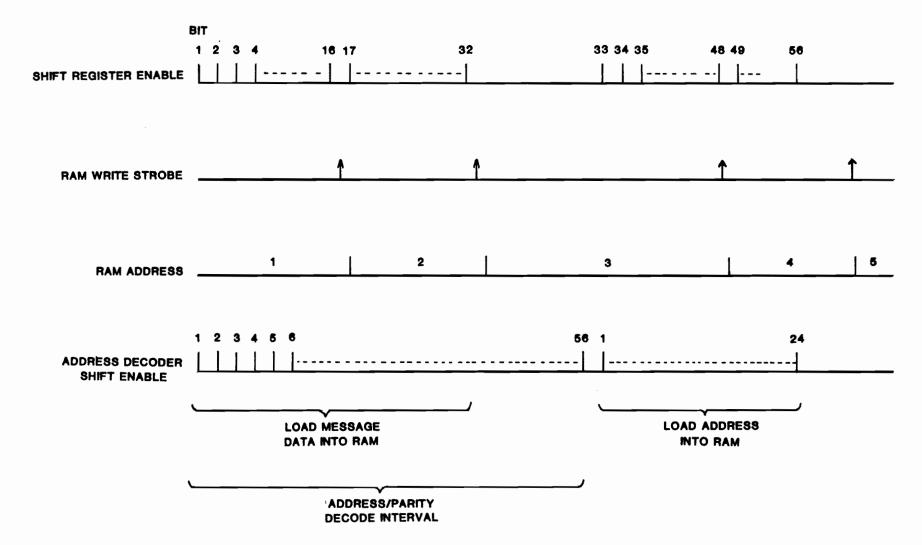

| 2.6-9            | Message processor timing                                       | 74  |

| 2.6-10           | Message processor timing                                       | 7.5 |

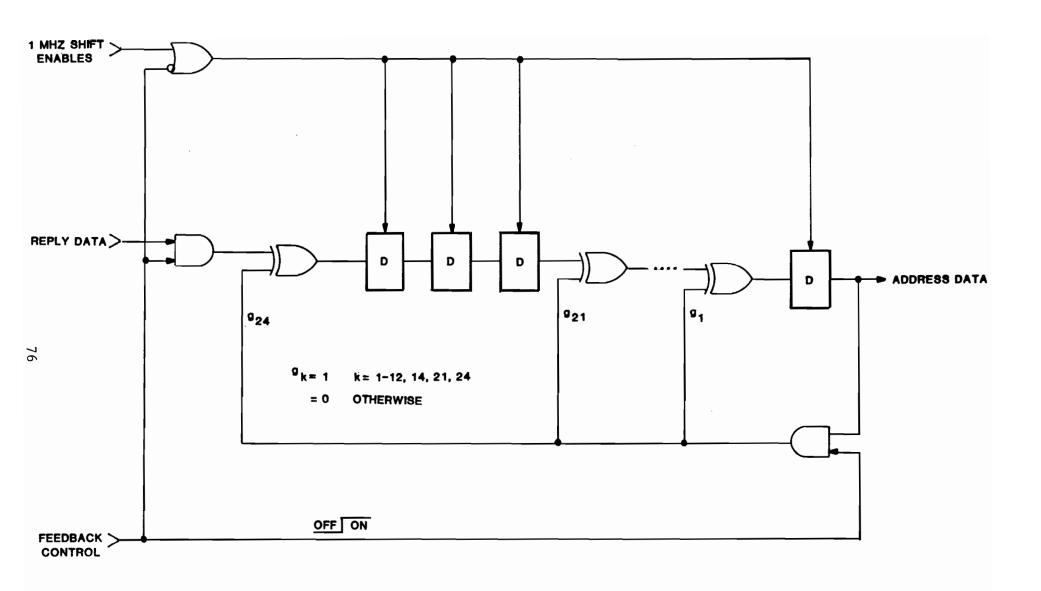

| 2.6-11           | Address decoder                                                | 76  |

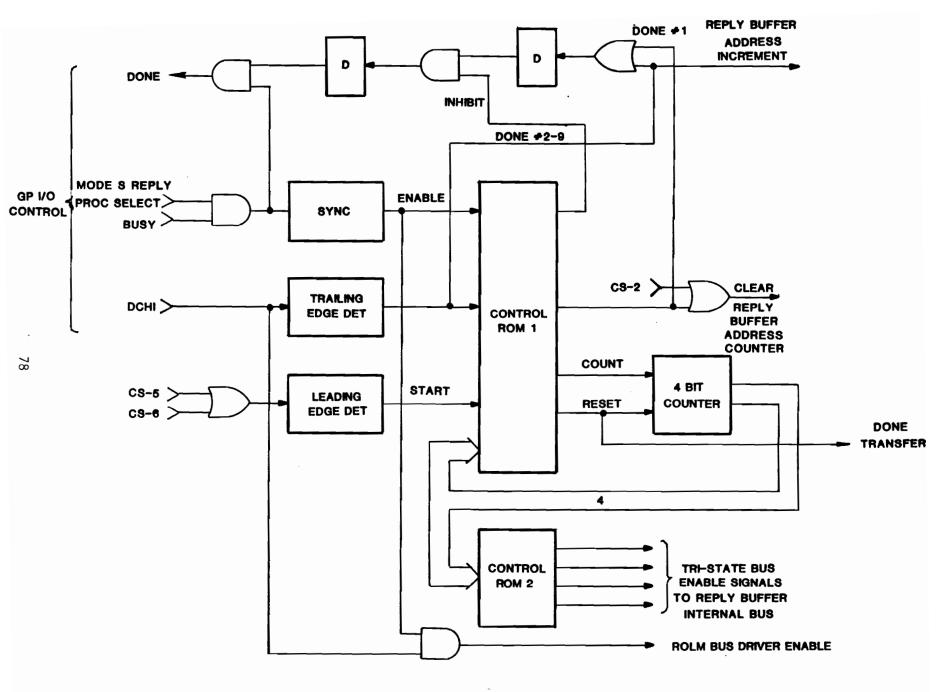

| 2.6-12           | Mode S I/O controller                                          | 78  |

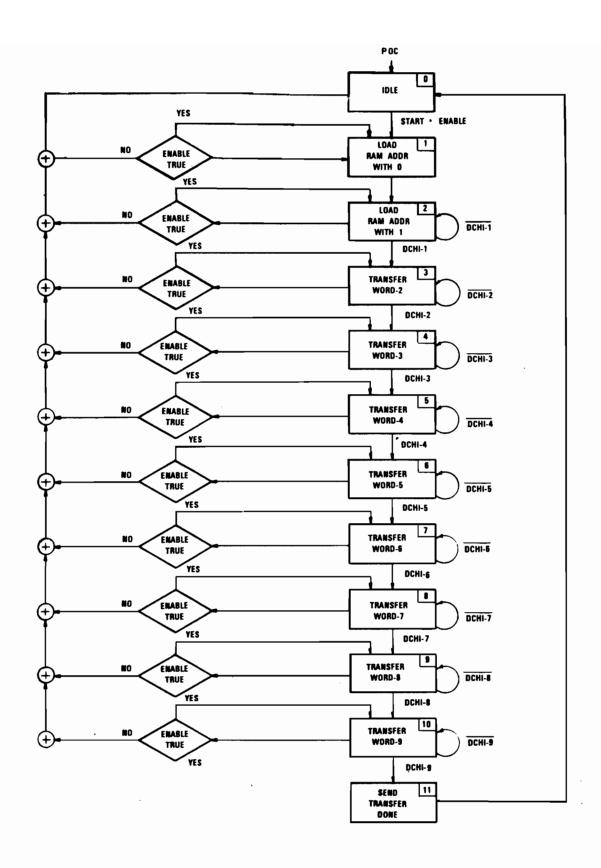

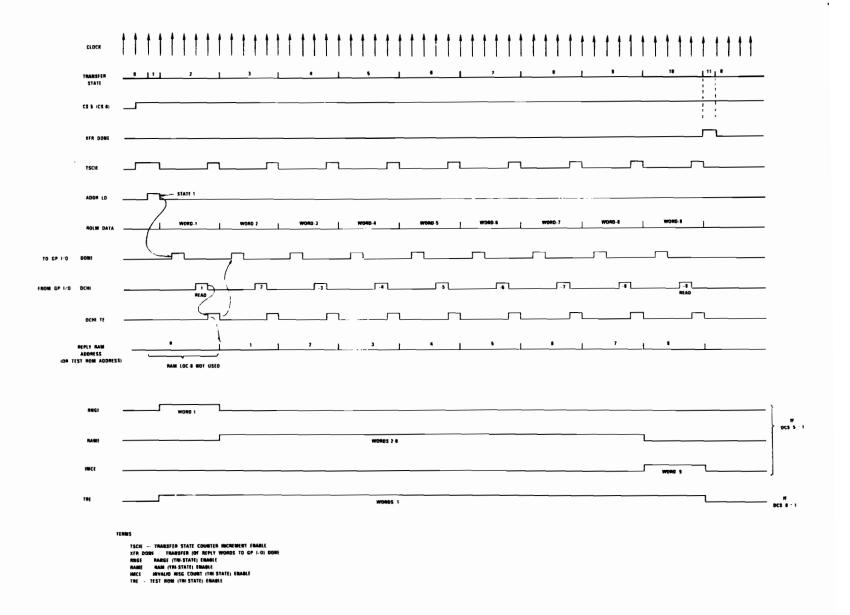

| 2.6-13           | Mode S I/O controller state diagram                            | 79  |

| 2.6-14           | Mode S I/O controller timing diagram                           | 80  |

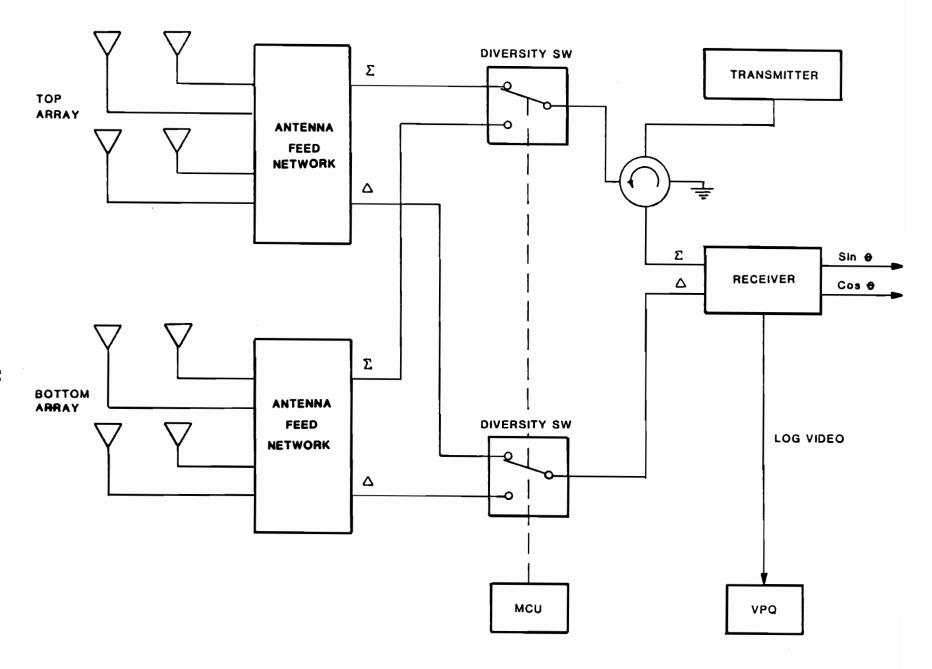

| 2.7-1            | TEU bearing augmentation - RF components                       | 81  |

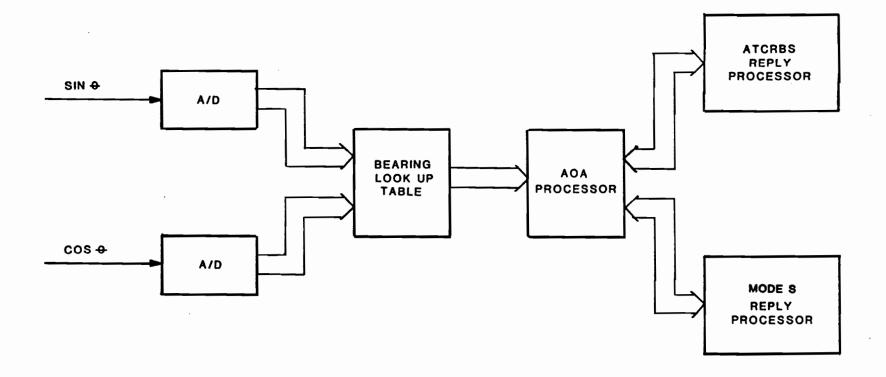

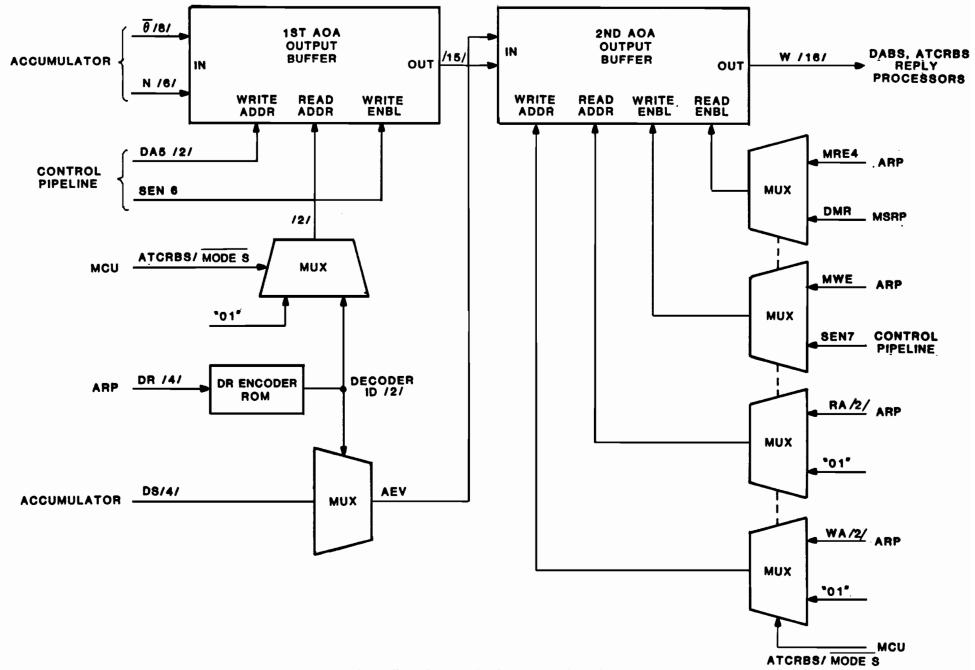

| 2.7-2            | TEU bearing augmentation - digital components                  | 82  |

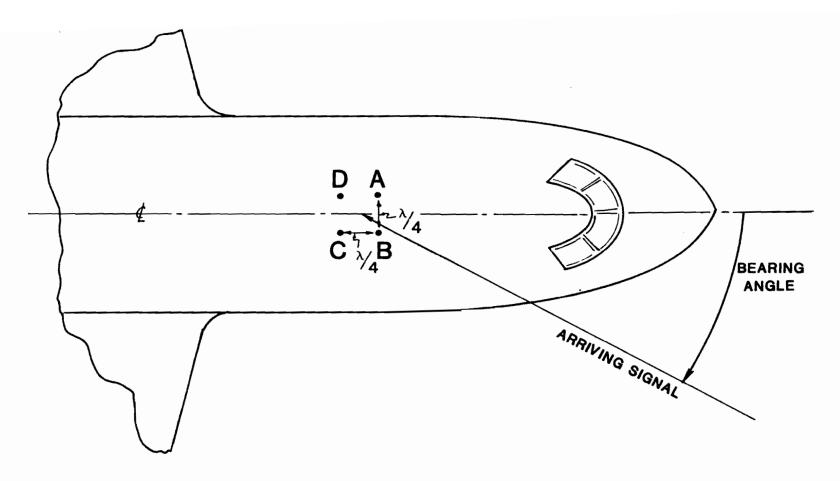

| 2.7-3            | AOA antenna orientation                                        | 84  |

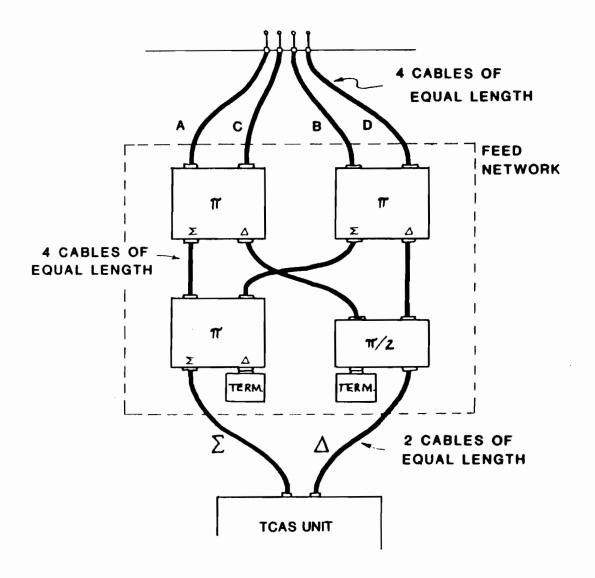

| 2.7-4            | AOA antenna feed network                                       | 85  |

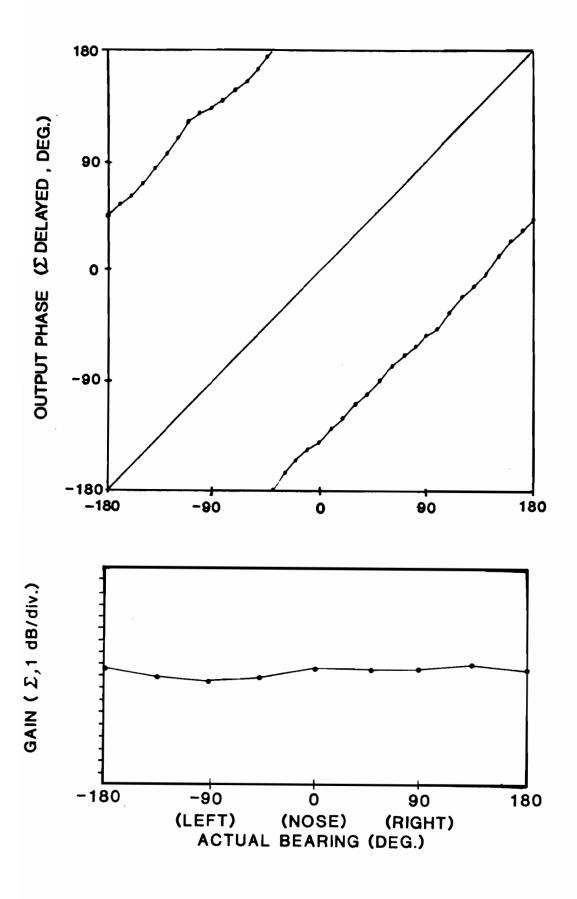

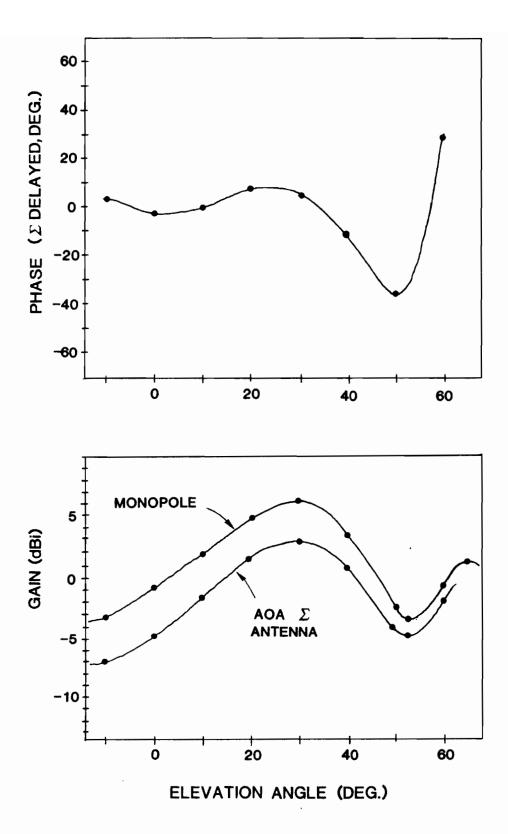

| 2.7-5            | Phase and amplitude response of the AOA antenna versus azimuth | 86  |

| 2.7-6            |                                                                | 87  |

| 2.7-0            | Phase and amplitude response of the AOA antenna                | 0.  |

| 2 77             | versus elevation angle                                         | 88  |

| 2.7-7            | TEU receiver block diagram                                     | 9(  |

| 2.7-8<br>2.7-9   | TEU AOA digitizer                                              | 9:  |

| 2.7-9<br>2.7-10  | AOA digitizer waveforms<br>TEU AOA processor                   | 92  |

| 2.7-10           | TEU AOA Processor - AOA controller                             | 94  |

| 2.7-11<br>2.7-12 | TEU AOA ATCRBS timing diagram                                  | 9.  |

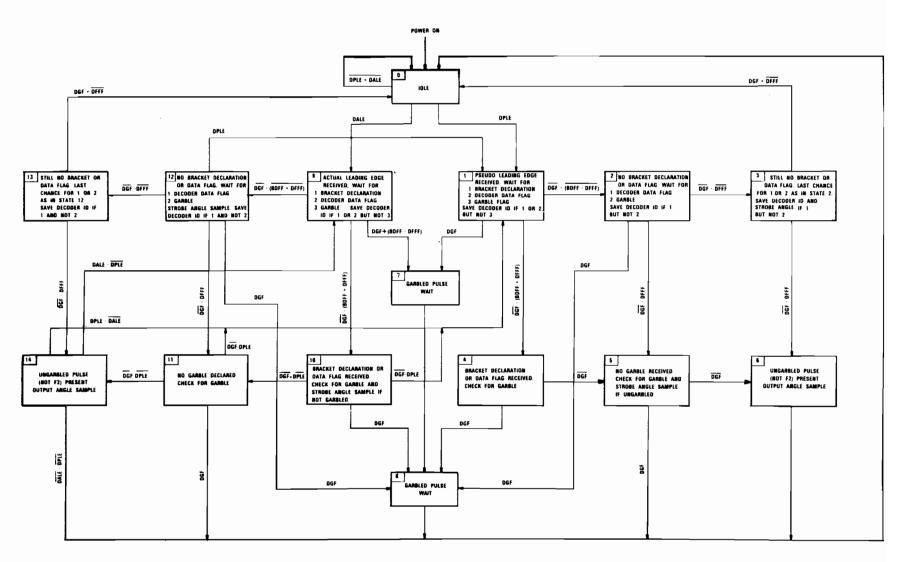

| 2.7-12           | TEU AOA ATCRBS state control diagram                           | 97  |

|                  |                                                                | 98  |

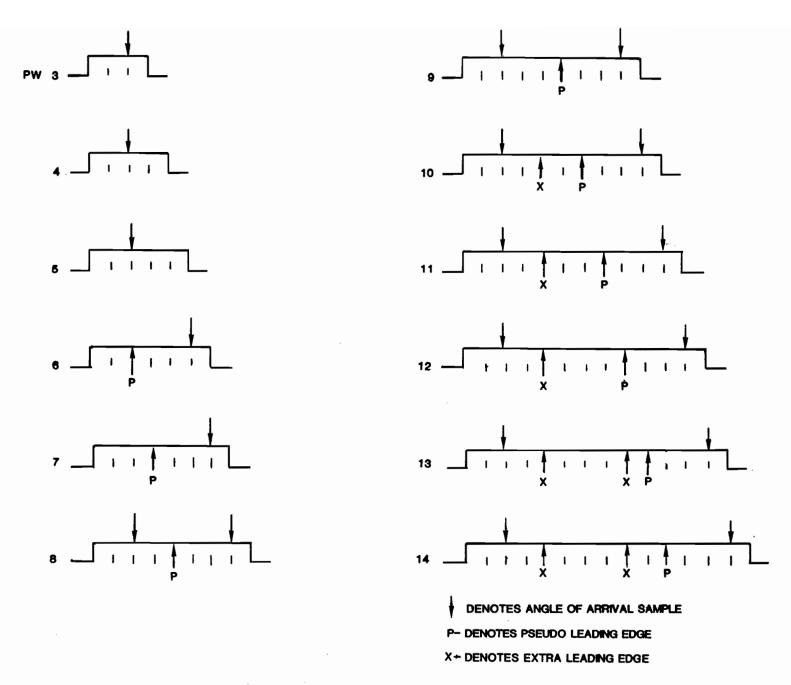

| 2.7-14           | AOA sampling of overlapped ATCRBS pulses                       | 100 |

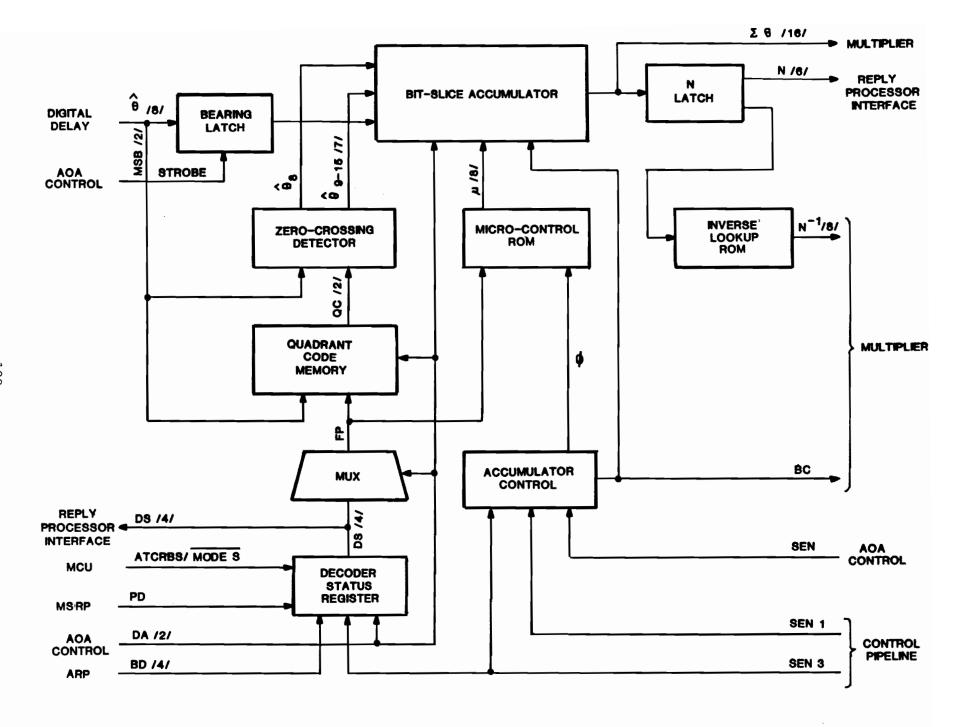

| 2.7-15           | AOA accumulator                                                | 100 |

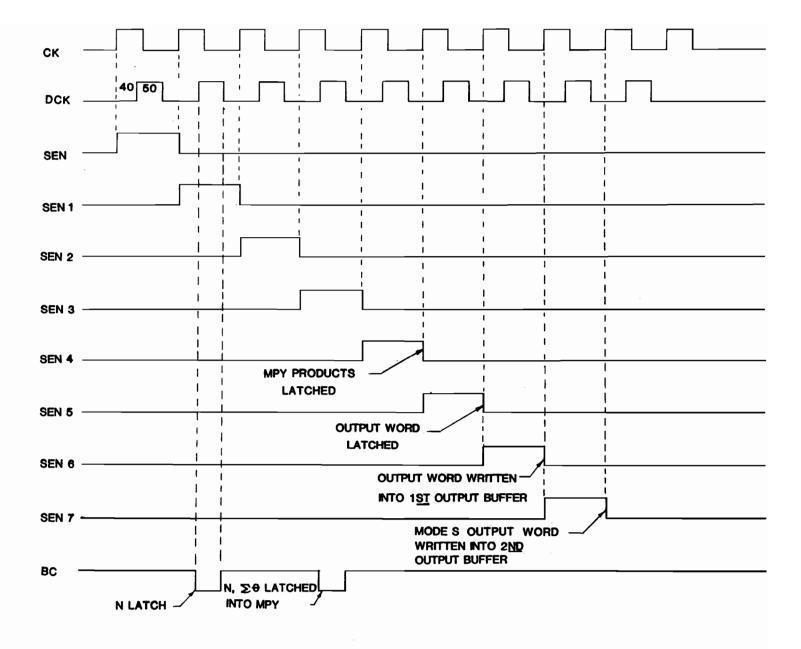

| 2.7-16           | TEU AOA accumulator timing diagram                             | 102 |

| 2.7-17           | AOA reply processor interface                                  | 10. |

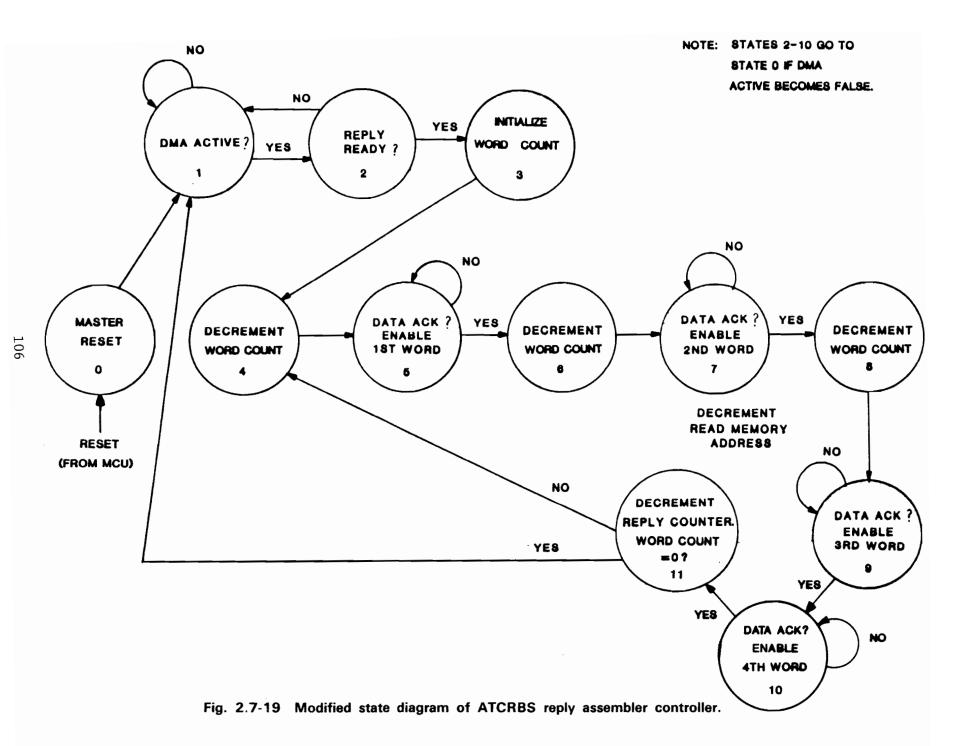

| 2.7-18           | Modified Mode S I/O controller state diagram                   | 10. |

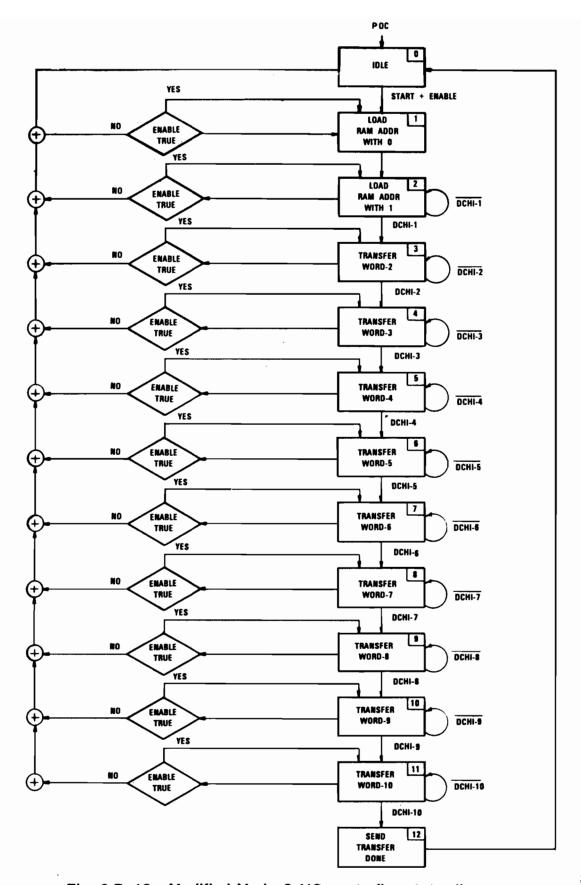

| 2.7-19           | Modified state diagram of ATCRBS reply assembler controller    | 106 |

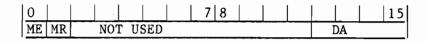

| 2.7-20           | AOA word format for ATCRBS and Mode S replies                  | 100 |

| 2.7-20           | ANA WOLD TOTHER TOT ATONDS and mode 3 replies                  |     |

| 2.9-1            | General purpose I/O interface                                  | 117 |

| TABLES         |                                                       |            |

|----------------|-------------------------------------------------------|------------|

| 2.3-1          | TEU RF Link Power Budget                              | 33         |

| 2.9-1<br>2.9-2 | GPIO Programmed I/O Summary GPIO Data Channel Summary | 112<br>114 |

#### 1.0 INTRODUCTION

#### 1.1 Purpose

This document describes the hardware design of the TCAS

Experimental Units (TEU's) built by Lincoln Laboratory for the Federal

Aviation Administration. These are experimental versions of TCAS (Traffic

Alert and Collision Avoidance System), a system designed to alert pilots to

nearby transponder-equipped aircraft and to assist them in avoiding

collisions.

The purpose in constructing the TEU's was to demonstrate a complete TCAS system that integrated the solutions to the many technical problems in areas ranging from elimination of multipath interference on the air-air link, to the modeling of aircraft trajectories and selection of appropriate commands, to the design of an appropriate interface between TCAS and the pilot. During the development process new problems were discovered and solutions developed, leading to the evolution of a large body of experience which is reflected in the standards that have been developed for commercial TCAS equipment.

#### 1.2 Summary of Operation

TCAS interrogates (at 1030 MHz) the radar beacons or transponders that are carried on all commercial and many general aviation aircraft. TCAS interrogates both the Air Traffic Control Radar Beacon System (ATCRBS) transponders that are the current standard transponders and also the Mode S transponders that will begin to be installed over the next decade. When interrogated these transponders reply (at 1090 MHz) after a fixed "turnaround" time. This allows the range to be determined. The reply contains data bits (12 for ATCRBS, 56 or 112 for Mode S). If the appropriate interrogation type is sent, the data in the reply contains a coded form of the aircraft's altitude. Some ATCRBS-equipped aircraft are not equipped with encoding altimeters, and their reply to an altitude interrogation is all zeros. Not all aircraft are equipped with transponders, and unequipped aircraft are not seen by the TCAS equipment.

From the measured range and encoded altitude in the replies TCAS derives range rate and altitude rate, and begins to track the other aircraft. If the track indicates that the other aircraft will pass too close to own aircraft within a short period of time (approximately 30 seconds, but this depends on the setting of the pilot's sensitivity level switch, own altitude, and sensitivity level commands sent from the ground) TCAS issues commands to the pilot. These may be either positive commands (climb, dive) or negative commands (don't climb, don't descend, don't climb faster than 1000 feet per minute, etc.). They are displayed as indicator lights on a modified Instantaneous Vertical Speed Indicator (IVSI). Positive commands light climb/dive arrows. Negative commands light yellow indicators around the periphery of the IVSI that act as speed limits. The pilot is advised to keep the IVSI needle out of the yellow regions.

TCAS units equipped to measure the bearing to other aircraft (also called the angle-of-arrival of the transponder reply, or AOA) can generate traffic advisory displays in a plan-view format. The aircraft displayed are normally limited to those within 5-10 nmi of own aircraft and in a band of altitudes within a few thousand feet of own altitude. This capability assists pilots in visually acquiring nearby aircraft. On the basis of visual information, they may then maneuver to avoid the need for collision avoidance commands, and may maneuver horizontally. The traffic advisory display also allows a pilot to better understand the local traffic situation, and therefore any commands that might be issued by the TCAS unit. It is able to display the bearing and range to non-altitude-reporting aircraft. TCAS cannot generate commands to avoid these aircraft due to the lack of altitude information, but can assist the pilot in visual acquisition if they happen to be nearly co-altitude.

The interrogation/reply link is complicated by several conditions. Both the interrogations and replies may be reflected from the ground. This is termed "multipath". It can cause a number of effects, including self-garbling of replies and false targets. Another problem with the link is that replies may overlap or garble. Garbling may be due to two or more aircraft being at the same range (synchronous garble) or due to replies which are responses to other interrogators, including ground interrogators. This is asynchronous garble, more usually called "fruit".

To divide up the ATCRBS aircraft population and reduce synchronous garble, especially when the TCAS unit uses an omni-directional antenna as do the TEU's, a technique called "whisper-shout" is used. Instead of a single interrogation, a series of interrogations are sent at increasing power levels. Each interrogation except the first is immediately preceded by a suppression pulse pair spaced 2 µ sec apart at a slightly lower (1-3 dB) power than the preceding interrogation. This suppression pulse pair causes ATCRBS transponders not to reply. The effect of this sequence is that the ATCRBS population is divided up based on link power margin. An ATCRBS transponder will typically reply to only two or three interrogations in the sequence. The lower powered interrogations will not be seen (will be below the transponder's threshold level). The suppression pulse pair preceeding the higher powered interrogations will suppress the transponder. At intermediate powers, the interrogation pulse pair will be above the transponder threshold but the suppression pair will be below threshold and the transponder will reply.

Multipath and fruit effects are eliminated by both hardware and software techniques. The primary hardware technique is a Dynamic Minimum Threshold Level (DMTL) which adjusts the receiver threshold such that the current reply is 6-9 dB above threshold. Multipath and fruit replies will usually be below this level and will not be seen by the receiver. Stronger fruit replies may capture the DMTL, however, and cause desired replies to be lost. This happens rarely, however, and the software tracking algorithms easily track through such misses.

Software techniques for dealing with multipath, fruit and other link problems are described in Ref. 1.

Mode S transponders are not affected by synchronous garble. Each transponder is interrogated individually by name (Mode S address), in contrast to the anonymous interrogations of ATCRBS. However, this introduces the problem of initially finding out what Mode S addresses are in the vicinity. This is done by passively listening to Mode S replies during times when neither ATCRBS nor Mode S surveillance is being performed. These replies may be replies to ground interrogators, replies to other TCAS aircraft or may be Mode S "squitter" replies which the transponder is required to emit once per second if it is not being interrogated.

For a more detailed TCAS summary see Ref. 2. References 3 and 4 give detailed technical discussions of the TCAS system design and validation. The ATCRBS surveillance algorithms used in the TEU correspond closely to those in Ref. 1, although that document contains some improved methods for tracking non-altitude-reporting aircraft and some other improvements that have not been incorporated in the flight software as of this date. The Mode S software demonstrated in the TEU corresponds, with the exception of recent refinements, to the software described in Ref. 5. Reference 6, Volume 2 describes the collision avoidance algorithms currently specified for TCAS. The algorithms in use in the TEU's as of this date are the earlier ones of Ref. 7 plus certain revisions made as flight experience was gained. References 6 and 8 are the standards developed for commercial TCAS installations.

#### 2.0 TCAS EQUIPMENT

#### 2.1 Major System Elements

The major components of a TCAS Experimental Unit (TEU) are shown in Fig. 2.1-1. These components are:

- A transmitter/receiver unit which generates interrogations at 1030 MHz and receives replies at 1090 MHz. The transmitter/receiver unit is capable, under computer control, of using either an antenna mounted on top of the aircraft or one mounted on the bottom. A reply log video signal is produced which is passed to the video pulse quantizer (VPQ) in the digital processing chassis. In the version of the TEU which provides bearing information (i.e., angle-of-arrival data) the receiver processes two signals from each antenna. The reply bearing information is contained in the relative phase of these two signals. In addition to log video, the AOA receiver produces two outputs called SINE and COSINE which are passed to the angle processor in the digital processing chassis.

- A digital processing chassis. As shown in Fig. 2.1-2, this contains:

- A modulation control unit (MCU) to control the transmitter and reply processors.

- A video pulse quantizer (VPQ) and video digitizer which process the log video returned from the receiver and provide several quantized signals to the reply processors.

- An ATCRBS reply processor.

- A Mode S reply processor.

- An optional Mode S transponder interface, which provides for air-air and air-ground communication using the Mode S data link.

- An optional angle-of-arrival (AOA) processor. This replaces the Mode S transponder interface (they are mutually exclusive due only to card slot limitations). In conjunction with an appropriate AOA receiver and antennas this provides the reply processors with information on the direction from which a reply was received.

- A General Purpose I/O (GPIO) interface. This provides a data channel or direct memory access interface (i.e., one where data transfers take place independently of the software, once initiated) for the MCU, reply processors, and Mode S transponder

FIG. 2. 1 -2. DIGITAL PROCESSING CHASSIS COMPONENTS AND INTERCONNECTIONS

interface. It also provides a programmed I/O interface (which requires explicit programming to transfer each word) for the encoding altimeter, the radar altimeter, the sensitivity level switch, and the IVSI display.

- A real-time clock

- A boot load ROM for initial system loading from a tape cartridge.

- An encoding altimeter, which provides altitude data both to the TEU processor and to the transponder.

- A Mode S transponder, which provides surveillance replies to both ground interrogators and other TCAS interrogators and also provides data link capabilities which are used for air-air and air-ground communication.

- An Instantaneous Vertical Speed Indicator (IVSI) modified to display collision avoidance commands.

- A sensitivity level control switch, which allows the pilot to control the "sensitivity" of the TEU by selecting among several settings of parameters in the collision avoidance logic.

- A microprocessor controlled CRT display, the Airborne Intelligent Display (AID), used to display traffic advisories to the pilot. Both tabular alphanumeric and plan view display formats have been used. The display is a modified color weather radar display, and remains able to perform weather radar functions. For more detail, see Ref. 12.

- Devices used for software debugging and data extraction:

- A standard keyboard/printer.

- A cartridge data recorder for program loading and data recording.

- A time-of-day (TOD) clock for time tagging the extracted data.

- An optional radar altimeter.

- A ROLM 1650 computer with 32768 words of memory and a 1-usec memory cycle time. The full TEU software system requires more than this amount of memory. Therefore, the Mode S surveillance software is normally not loaded.

- A ROLM 1650 I/O expansion chassis, with CPU front panel. This provides for the usual CPU manual controls used for debugging, as well as additional I/O interface slots for interfaces to the keyboard/printer, cartridge data recorder, time-of-day clock, and the AID.

An auxiliary interface box (not shown in Fig. 2.1-1) which can be substituted for the I/O expansion chassis. It provides all the functions of the I/O expansion chassis except for the CPU front panel and the keyboard/printer interface. It is used with TEU's whose sole purpose is data taking and not software or hardware debugging.

The operation of the components of the transmitter/receiver and of the digital processing chassis will be discussed in the following sections. The other TEU components will be discussed only to the extent required to explain the operation of the transmitter/receiver and the digital processing chassis.

#### 2.2 Modulation Control Unit

#### 2.2.1 Function

The Modulation Control Unit (MCU) is the interface by which the CPU controls the transmission of interrogations and the processing of replies. The CPU transfers a block of control information to the MCU via the data channel to initiate a transmit/receive operation. The MCU then generates the appropriate control and timing signals for the transmitter, video pulse quantizer, angle-of-arrival processor, and ATCRBS and Mode S reply processors. The MCU also accepts range strobes from the ATCRBS and Mode S reply processors and uses these to latch the current range clock value for use by these processors. At the end of the interrogation listening window, it sends a range gate close pulse to the GPIO interface, triggering the range gate close interrupt. A final MCU function is to prevent the transmitter duty cycle from exceeding safe limits. It does this by ignoring any modulation requests that occur too soon after a previous transmission. A 2-msec interval is required after ATCRBS transmissions and a 16-msec interval following Mode S transmissions.

#### 2.2.2 Programming

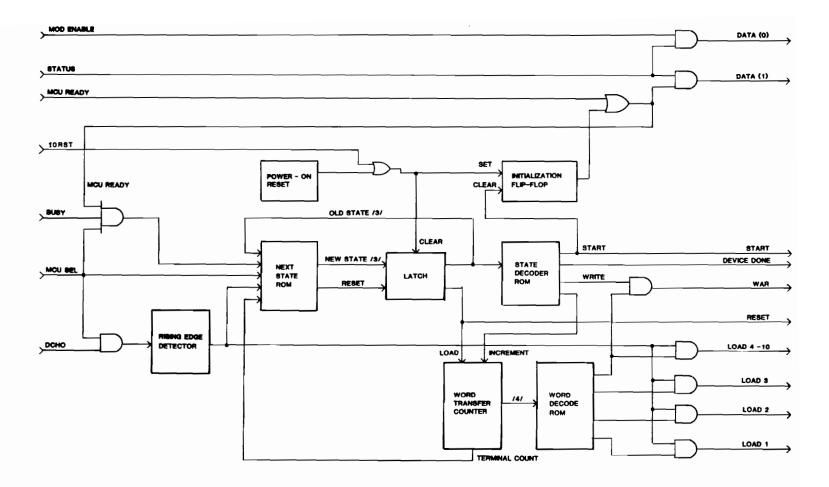

The MCU's operation is controlled by means of 10-word command blocks transferred from the CPU via the GPIO data channel interface. GPIO data channel programming is discussed in greater detail in Section 2.9. The software must first determine whether the MCU is ready to receive a command. This is done by reading the GPIO status via a DIB instruction. Note that the MCU does not have to be the selected GPIO device in order to read the MCU status. The status word returned contains two MCU status bits. If the MCU Ready (MR) bit (bit 1) is 1, the MCU is ready to receive a command block. However, if the command block specifies an interrogation, as opposed to a squitter listening function, the Modulation Enabled (ME) bit (bit 0) must also be 1 or else the MCU will not modulate the transmitter.

Before transferring the command block, any GPIO data channel transfer in progress must be terminated and the GPIO device address must be set to route data channel transfers to the MCU. Then the data channel buffer address and word count are initialized and a START pulse is issued to initiate the transfer. The software must then wait until the transfer is complete. This is signalled by the setting of DONE, clearing of BUSY, and the generation of an interrupt from device 7. The I/O skip instructions can be used to test

BUSY or DONE, or the interrupt can be used to trigger further processing. Given the short transfer time, and the fact that the GPIO channel must be reallocated immediately to one of the reply processors, it is usually best for the software to idle using an I/O skip instruction and with the device 7 interrupt disabled until the transfer is complete.

The format of the 10-word command block is shown in Fig. 2.2-1, along with an explanation of each of the fields.

#### 2.2.3 Operation

#### 2.2.3.1 Summary

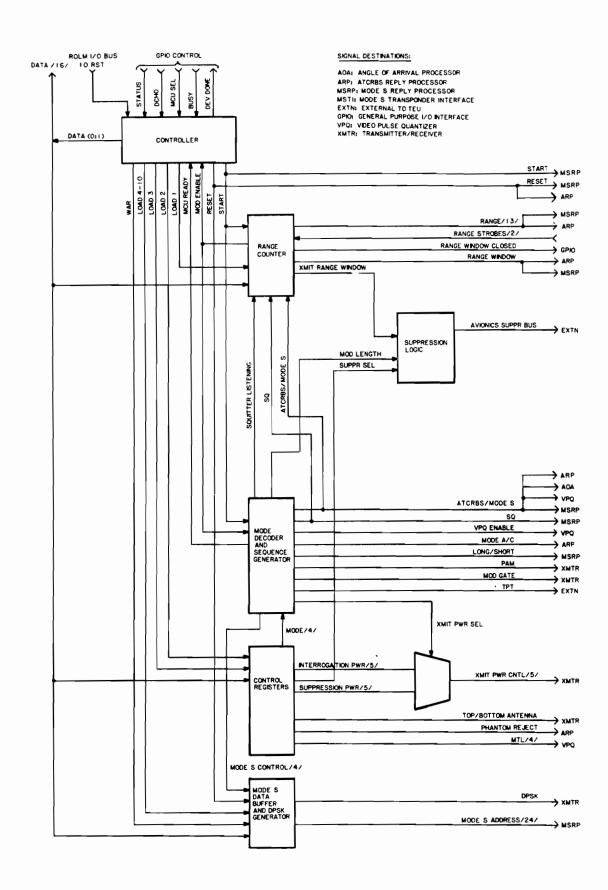

An overall MCU block diagram is provided by Fig. 2.2-2. When the GPIO data transfer is started by the software, this is signalled over the BUSY line to the MCU controller. The controller then goes through a series of states which transfer the 10 command words from the CPU memory and load them into appropriate MCU registers. The listening window (first word) is loaded into the range counter, the second and third words into the two control registers, and words 4 through 10 are loaded into the Mode S data buffer memory.

When the command block transfer is completed the MCU controller issues a START pulse. This initiates the MCU command processing as well as being sent to the ATCRBS and Mode S reply processors. The START pulse initializes the range counter, which begins incrementing once every 125 ns. The range window counter also starts incrementing at this rate starting from the initial listening window value. Finally, the mode decoder and sequence generator also is initialized and its interval timing counter begins incrementing at the same 8-MHz rate.

The control registers hold all the data regarding the nature of the interrogation and the type of reply processing required. Some of this data directly affects control lines to other devices. The mode information is decoded to create other external control signals and also to control the sequence generator, which provides time-varying signals. For Mode S interrogations, the sequence generator in turn controls the Mode S data buffer and DPSK generator which generates the DPSK data modulation signal for the transmitter and provides the MODE S ADDRESS data to the Mode S reply processor.

The suppression logic places the AVIONICS SUPPRESSION BUS in the suppressed state (+28 volts) at the START pulse of any interrogation. Squitter listening mode does not cause suppression. The bus is held in the suppressed state until either the interrogation is completed or the listening window closes. Selection between these two modes is done by software via the SC bit of the MCU control block (Fig. 2.2-1).

When the range window counter counts up to zero, the RANGE WINDOW closes and the RANGE WINDOW CLOSED pulse is sent to the GPIO interface, causing an interrupt of the CPU. This terminates reply processing. However, the range

|        | 0                                            | 15    |

|--------|----------------------------------------------|-------|

| WORD 1 | LISTENING INTERVAL                           |       |

| 2      | SC MTL CONTROL /////////// PB ///////        | ///// |

| 3      | INTERROGATION PWR SUPPRESSION PWR MCU MODE D | 1///  |

| 4      | 1                                            | 16    |

| 5      | 17 Mode S UPLINK DATA                        | 32    |

| 6      | 33                                           | 48    |

| 7      | 49 56                                        | 64    |

| 8      | 65                                           | 80    |

| 9      | 81                                           | 96    |

| 10     | 97                                           | 112   |

#### LISTENING INTERVAL

Receiver listening interval in 2's complement format. LSB increment = 125 ns. The listening window must be set longer than the nominal listening range to account for various hardware delays. An additional  $87 \, \mu \, \text{sec}$  should be allowed in ATCRBS modes, and an additional  $230 \, \mu \, \text{sec}$  in Mode S.

SC

Suppression control.

- 0 = the external avionics suppression line will be held in the "suppress" (+28V) state for the duration of the listening window.

- l = the external avionics suppression line will be held in the "suppress" state from TPT to the end of the interrogation (approximately  $30~\mu\,\text{sec}$ ).

MTL CONTROL

Minimum threshold level control for the VPQ. LSB increment = 2 dB.

0 = -77 dBm referred to the TEU 15 = -47 dBm antenna input port

PВ

Phantom rejection control for the ATCRBS reply processor. A phantom is a false reply created due to the accidental spacing of code and/or framing pulses of two real replies.

0 = Accept all replies

1 = Reject all phantoms

Fig. 2.2-1. MCU control block format.

### DEFINITION OF FIELDS (Continued)

| FIELD              | SIGNIFICANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERROGATION PWR  | Transmitter power attenuator control for the P1-P3-P4 interrogation pulses. LSB increment = 1 dB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | 0 = 31-dB Attenuation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 31 = 0-dB Attenuation. The nominal power at the transmitter output connector is +57 dBm in this case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SUPPRESSION PWR    | Transmitter power attenuator control for S1 S2 suppression pulse pair. LSB increment = 1 dB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | 0 = 31-dB Attenuation $31 = 0-dB$ Attenuation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MCU MODE           | MCU mode select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 0 0 0 0       Mode A, P4, no suppression         0 0 0 1       Mode C, P4, no suppression         0 0 1 0       Mode A, P4, suppression         0 0 1 1       Mode C, P4, suppression         0 1 0 0       Mode A, No P4, no suppression         0 1 0 1       Mode C, No P4, no suppression         0 1 1 0       Mode A, No P4, suppression         0 1 1 1       Mode C, No P4, suppression         1 0 0 0       Long Mode S         1 0 1 0       Short Mode S         1 0 1 1       Unused         1 1 0 1       Unused         1 1 1 0       Unused         1 1 1 1       Unused         1 1 1 1       Terminate squitter listening |

| D                  | Diversity Switch Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 1 = Top Antenna<br>0 = Bottom Antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MODE S UPLINK DATA | Data and address for the Mode S modes. The last 56 bits of this field are ignored for short Mode S transmissions. This entire field is ignored for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Fig. 2.2-1. MCU control block format (Cont'd).

supplied.

ATCRBS and squitter listening modes but it must be

FIG. 2. 2 -2. MCU BLOCK DIAGRAM

counter continues to count, timing out either 2 msec (for an ATCRBS interrogation) or 16 msec (for a Mode S interrogation) at which point MODULATION ENABLED is asserted. At that point both MCU status bits will indicate that the MCU is ready for another interrogation command.

When the command block indicates squitter listening mode, a slightly different procedure is followed. The sequence generator is not activated, since no transmission is sent. Similarly, the range and range window counters are not started. The RANGE WINDOW is opened at the START pulse. The ATCRBS/Mode S line indicates Mode S, but the SQ line indicates to the Mode S reply processor that squitter reply processing is desired. This disables the Mode S address checking logic in the Mode S reply processor. The AVIONICS SUPPRESSION BUS is left in the unsuppressed state.

In squitter mode the RANGE WINDOW remains open, as the range window counter is not incrementing. Therefore, to stop squitter listening and close the range window a new MCU control block must be output by the software with the "stop squitter listening" mode. This must be done prior to sending any command block that generates an interrogation. This also allows the Mode S reply processor to terminate properly.

#### 2.2.3.2 MCU Controller

The MCU controller is a standard state controller. The outputs and the next state are determined by the inputs and the current state. A PROM provides the translation from input/current state to output/next state. A register is used to latch the next state. A block diagram of the controller is shown in Fig. 2.2-3 and a state diagram for the controller is shown in Fig. 2.2-4. At power-on, the controller is initialized to state 0, from which it immediately passes to state 1 after issuing a RESET. It waits in state 1 until the conditions for a data channel transfer are satisfied. issues a RESET and begins the transfer. In state 3 it issues the DEVICE DONE pulse to request a word transfer from the GPIO interface. It waits in state 4 until the resulting DCHO signal is received, at which point it enters state 5 to read the data. It then returns to state 3 for the next word, or, if the last word has been transferred, it goes to state 6 which issues the START pulse to initiate the interrogation. An auxiliary word count register is used by the controller to route the data channel words to the appropriate This is incremented in state 3. Note that the WRITE signal generated in state 5 does not control the loading of registers. Its only function is to increment the Mode S data buffer's write address register at the appropriate times. As can be seen in Fig. 2.2-3, WRITE is gated by LOAD4-10 to produce the WAR signal that increments the address counter.

#### 2.2.3.3 Mode Decoder and Sequence Generator

Figure 2.2-5 is a block diagram of the mode decoder and sequence generator. The mode decoder is a PROM which generates control signals based on the current mode value as received from the MCU control registers. The sequence generator consists of a sequence counter, some PROMs which store the various timing signals, multiplexers for selecting the desired signals, and

FIG. 2. 2 -S. MCU CONTROLLER BLOCK DIAGRAM

FIG. 2. 2 -4. MCU CONTROLLER STATE DIAGRAM

FIG. 2. 2 -6. MCU MODE DECODER AND SEQUENCE GENERATOR

latches for synchronizing and holding the outputs. The sequence counter is loaded at the START pulse, if modulation of the transmitter is allowed. It counts at an 8-MHz rate through a 64-µsec sequence. At the end of this time, the MCU READY signal becomes true, and disables the counter. The counter output is used to address the PROMs, which generate the signals shown. Particular signals are selected by the multiplexers based on control signals from the mode decoder. The MOD LENGTH signal determines the length of the PAM modulation, and therefore whether or not the P4 pulse, present in all the ATCRBS PAM outputs from the PROMs, will be output or inhibited at the multiplexer. The MOD GATE signal is required by the transmitter before modulation is initiated. The circuit shown assures that MOD GATE goes high one clock before PAM, and stays high until one clock after PAM goes low.

Figure 2.2-6 shows the timing of the various PROM outputs. The timing shown is at the output of the sequence PROMs. The relative timing of some signals changes before their point of use due to differing numbers of delaying flip-flops along their paths.

#### 2.2.3.4 Mode S Data Buffer and DPSK Generator

Figure 2.2-7 is a block diagram of this portion of the MCU. When the MCU controller initiates the transfer of a 10-word command block over the data channel, it pulses the RESET line, setting the buffer address register to its initial state. As words 4 through 10 of the command block are transferred, LOAD4-10 is pulsed by the MCU controller as each word is available on the DATA lines. After each LOAD4-10 pulse, a WAR pulse is sent which allows the buffer address register to increment by one. In this way, all the Mode S data bits are loaded into the buffer memory. These words are loaded into the buffer memory whether or not the control block's mode field indicates a Mode S interrogation.

Next, unless the mode field of the MCU control block selected squitter listening, the sequence generator will supply the various control signals for the DPSK modulation. See Fig. 2.2-6 for the timing of these signals. The sequence begins with the arrival of simultaneous CLEAR and SHIFT REG CLK pulses. CLEAR puts the output of the Adr/Msg multiplexer in a high impedance state, allowing the pull-up resistor on the output to drive the input to the toggle flip-flop high. SHIFT REG CLK is never used directly as a clocking signal, but rather always enables either the system's 8-MHz CLOCK signal, or its complement CLOCK. In this case, it allows the toggle flip-flop to clock, toggling its output and causing a phase shift. This is the sync phase reversal of the Mode S DPSK modulation. The analog timing adjustment delay is used to precisely align the DPSK phase shifts relative to the PAM modulation.

The CLEAR pulse also resets the buffer address register to its initial value and, after a one clock delay, clears the tapped shift register used for the Mode S parity encoding function.

FIG. 2. 2 -7. MODE 8 DATA BUFFER AND DPSK GENERATOR

The SHIFT/LOAD and SHIFT REG CLK signals then control the operation of the parallel/serial converter, the parity generation circuitry, the Mode S address shift register and the DPSK toggle flip-flop in a straightforward manner. During the message part of the Mode S transmission (the first 32 bits for a short message, or 88 bits for a long Mode S interrogation) the output of the parallel-to-serial converter directly drives the DPSK toggle flip-flop. It also feeds into the parity encoding process as one of the inputs of the modulo-2 summing circuit, the output of which feeds into the tapped shift register.

During the address portion of the transmission, the DPSK toggle flip-flop is driven by the output of the modulo-2 summing circuit, which provides the encoded Mode S address overlaid (modulo-2 summed with) the parity code developed during the message portion of the transmission. The output of the parallel-to-serial converter is directly routed to the input of the tapped shift register.

For detailed information on the design of the Mode S uplink message encoder and on the properties of the code, please refer to Ref. 10.

During the address portion of the message, the output of the parallel-to-serial converter is also shifted directly into the Mode S address register. It is held there until the next MCU transmission. The Mode S ADDRESS output is used by the Mode S reply processor to determine if a reply is from the interrogated transponder.

Note that the DPSK modulation signal is generated for any MCU control block except for those specifying squitter listening. For ATCRBS interrogations, however, the PAM signal to the transmitter is not present (except possibly for the P4 pulse) during the DPSK modulation, and so no waveform is transmitted. DPSK modulation during the P4 pulse does not affect any of the uses of the P4 pulse.

#### 2.2.3.5 Range Counter

The range counter circuitry (Fig. 2.2-8) actually involves two counters. The first provides the system's 8-MHz range clock, and the second counts out the range window specified by the software in the first word of the MCU control block.

The range window counter is loaded from the data bus at the LOAD-1 signal generated by the MCU controller. The value loaded is the two's complement of the desired range window interval, and has an LSB of 125 nsec. On receipt of a START pulse while the MCU mode is other than SQUITTER LISTENING, the two J-K flip-flops will be cleared. In addition, if MOD ENABLE is true, the range clock is initialized. The initial value loaded depends on whether an ATCRBS

FIG. 2. 2 -8. RANGE COUNTER

or a Mode S transmission is being sent. The values loaded are such that the range clock overflows 2 msec after the START pulse for an ATCRBS interrogation and 16 msec after the START pulse for a Mode S interrogation.

The clearing of the flip-flops opens the RANGE WINDOW. This also enables the range window counter. When this counter overflows, it sets its associated flip-flop, thereby closing the RANGE WINDOW. It also generates the RANGE WINDOW CLOSED pulse which goes to the GPIO circuitry and triggers an interrupt of the computer.

In the case of squitter listening, the flip-flops do not clear at the START pulse. Instead, the SQ signal opens the RANGE WINDOW. This signal must be removed, by issuing a "Stop Squitter Listening" command block to the MCU, in order to close the RANGE WINDOW.

The least significant bits of the range clock are sampled into the range latch when an appropriate RANGE STROBE arrives. Those bits are all 0 at the START pulse, and count time in 125-nsec increments from that pulse.

#### 2.2.3.6 Suppression Logic

Figure 2.2-9 shows the avionics suppression circuit. The SUPPRESSION SELECT line, which is controlled via the SC bit in the MCU control block, determines whether the MOD LENGTH or XMIT RANGE WINDOW signal drives the suppression bus. If MOD LENGTH is selected, suppression ends at the end of the interrogation. If XMIT RANGE WINDOW is selected, suppression lasts for the entire listening window.

While these were the two options supplied in the TEU for experimental purposes, it has since been determined that an intermediate suppression length is best. Suppressing the other on-board avionics serves two purposes:

- a) It prevents the Mode S transponder from replying to its own ship's TCAS interrogations by suppressing the transponder during the interrogation.

- b) It prevents the transponder from replying to interrogations reflected from the ground after transmission from own TCAS. This is accomplished by extending the suppression into the listening window. Suppressing for the entire listening window is an extreme form of this.

Suppressing for the entire listening window has the advantage that it prevents all replies from own ship's transponder during the listening window, and so eliminates this powerful interference source. However, in an operational TCAS it would unacceptably reduce the transponder's round reliability as seen by ground interrogators. Therefore a shorter suppression interval has been chosen for operational TCAS systems that prevents responses as in (a) and (b) above, but does allow for the possibility that the transponder might reply to a ground interrogator such that it interferes with a TCAS listening interval.

FIG. 2. 2 -9. SUPPRESSION LOGIC

#### 2.3 Transmitter/Receiver

In this section, the TEU transmitter/receiver circuitry for a non-AOA TEU is described. The additional circuitry required for AOA measurements is discussed in Section 2.7.

The TEU transmitter/receiver, Fig. 2.3-1, contains the following functional subunits:

- a) Microwave signal source

- b) Transmitter chain

- c) Antenna interface and transmitter monitor

- d) Receiver chain

All of the power supplies necessary to power the RF unit are housed in the TEU Digital Processor assembly.

#### 2.3.1 Microwave Signal Source (1030 MHz)

A phase-locked, temperature controlled crystal oscillator, stabilized to within  $\pm$  0.0005% of the nominal frequency, and a solid state multiplier chain generate the L-band transmitted carrier frequency. The output power level of the oscillator multiplier chain is high enough to permit the insertion of an L-band circulator and a 10-dB pad between the generator and the output ports to the transmitter and receiver. The isolation, and the use of an absorptive rather than a reflective pulse amplitude modulation (PAM) switch, provide the carrier frequency stability required by the TCAS National Standard.

The microwave source is enclosed in a shielded enclosure to minimize leakage. This is important because of the possibility of interference with the operation of the co-located airborne transponder whose receiver is tuned to the same frequency (1030 MHz).

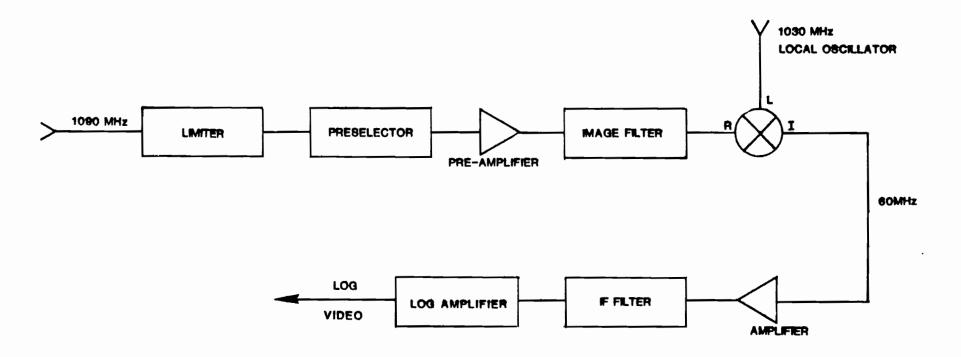

The same 1030-MHz frequency source is used to drive the transmitter and to provide the receiver's local oscillator, so one-half of the microwave source output power is directed to the transmitter chain, and the other half is directed to the "L" port of the receiver's down-converter. The latter, mixed with the transponder's reply frequency (1090 MHz), generates the 60-MHz intermediate frequency (IF).

#### 2.3.2 Transmitter Chain

The transmitter chain (Fig. 2.3-2) consists of

- a. DPSK and PAM modulators

- b. Microwave power module

- c. Digital attenuator

- d. Bandpass filter

Fig. 2.3-1 TEU transmitter/receiver block diagram.

Fig. 2.3-2 Transmitter chain block diagram.

#### 2.3.2.1 PAM/DPSK Modulators

Two types of modulators are required: a pulse amplitude modulator (PAM), and a differential phase-shift keyed (DPSK) modulator. The PAM modulator determines the duration of the transmitted microwave pulse. It consists of an absorptive type switch with an off/on ratio of 110 dB.

The DPSK modulator consists of a double balanced mixer and a video driver. The microwave signal is fed to the "L" port and a bipolar signal is fed to the "I" port. As long as the video signal magnitude is larger than zero the microwave signal is transmitted from the "L" to the "R" port. However, to minimize insertion loss, the "I" port is driven at approximately 20 mw. Every time the polarity of the video signal at the "I" port is changed the phase of the microwave signal at the "R" port is reversed.

Since the bandwidth of the double-balanced mixer is large relative to the system's bandwidth, the DPSK transition is determined by the rise-time of the driver's video pulse and by the bandwidth of the system. The TCAS National Standard requires that these transitions be completed within 80 nanoseconds, 10 degrees to 170 degrees.

#### 2.3.2.2 Microwave Power Module

The microwave module consists of five electron tubes providing a 47-dB power gain at 1030~MHz. The first three stages are gated while the last two are RF-driven. The output power of the L-band amplifier chain can be adjusted from 1- to 2-KW peak by setting the magnitude of the high voltage, and by setting filament voltages for optimum electron emission consistent with specified tube life. The maximum microwave power required at the input of the power module is +16~dBm (40~mw), resulting in an available power gain of 47~dB.

The power module is energized by the aircraft's 28-volt source; a DC-to-DC inverter is used to provide both heater and high voltages. Because vacuum tubes have a tendency to arc, stored energy (E = 1/2 CV<sup>2</sup>) is limited by limiting the value of the capacitor to that needed to satisfy microwave pulse rise-time requirements. A pulse-modulated, current-limited, power supply provides the required energy and assures that the maximum pulse droop is within 1-dB. In the event that an arc occurs, or the pulse width is extended beyond 30- $\mu$  sec, or the PRF is accidentally increased to a rate unsafe for the tubes to handle, the power supply automatically shuts off, resuming operation when safe conditions are re-established.

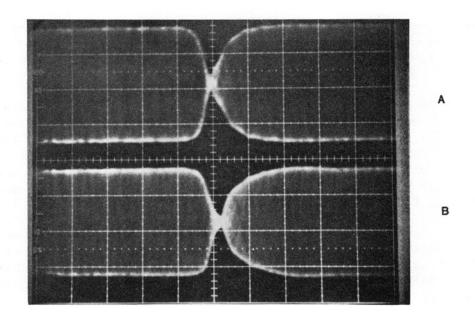

Typical performance of the transmitter is shown in Fig. 2.3-3 which illustrates a transition of the DPSK modulation. The upper waveform indicates the input to the l-kW amplifier, and the lower waveform the output of the amplifier. The horizontal scale is 50 nanosecond/cm. It can be seen that the bandwidth of the transmitter is adequate to achieve the time limit allowed by the National Standard for 180° DPSK phase reversals.

HOR. 50 NANOSEC /cm.

Fig. 2.3-3. Power module response to DPSK transition.

# 2.3.2.3 Digital Attenuator

The full output of the microwave power module is passed through a 5-bit digital attenuator, providing a least significant bit attenuation change of 1 dB and most significant bit attenuation change of 16 dB. This attenuator passes 1-Kw peak power, 2-watts average, and provides 32 values of attenuation in 1-dB steps. Maximum insertion loss is 1.5 dB; switching time is 1.0 microsecond. A 5-bit digital switch driver is provided with the attenuator.

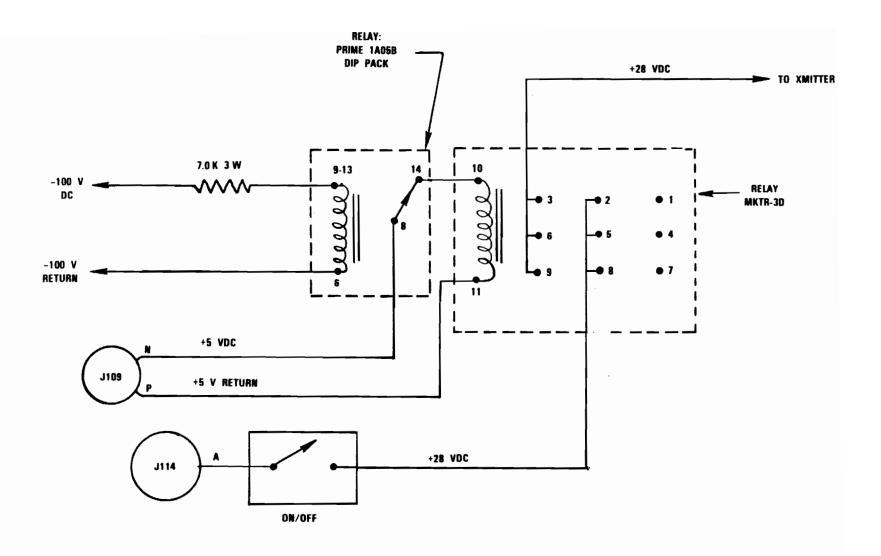

Since the attenuator is a cold switching unit, it must not be switched while microwave energy is passing through it. The digital control system assures that this is so. In addition, an interlock is included to ensure that critical supply voltages (plus 5 volts and minus 100 volts) are present before high microwave power is applied to the attenuator. This interlock is shown in Fig. 2.3-4.

# 2.3.2.4 Bandpass Filter

This filter is centered at 1030 MHz, has a bandwidth of 20 MHz, an insertion loss of 0.5 dB, and provides 60-dB (with respect to band-center peak power) attenuation at the receive frequency (1090 MHz.)

# 2.3.3 Antenna Interface and Transmitter Monitor

The antenna interface and transmitter monitor consists of the following components:

- a) A 4-port circulator. This device acts as diplexer, connecting transmitter, receiver and antennas. It provides 40-dB isolation between transmitter and receiver.

- b) A transmitter monitor coupler and detector. A 30-dB RF coupler terminated with a diode detector permits monitoring the transmitter on an oscilloscope.

- c) A diversity switch. This solid-state SPDT switch connects either the top-or bottom-mounted antenna, as commanded by the computer software. It will handle 1-Kw peak power, 2-watts average, and provides 20-dB inter-channel isolation. Switching time is 10 microseconds.

- d) Two antenna low pass filters. These low pass filters prevent the radiation of harmonics generated by the diversity switch.

The TEU antennas are standard quarter-wave monopole stubs, with an approximately omni-directional radiation pattern in the horizontal plane.

#### 2.3.4 Receiver Chain

The receiver chain (Fig. 2.3-5) consists of:

a) A receiver input limiter. This is a reflective-type device used for receiver input protection. It can withstand l-kW peak pulses

Fig. 2.3-4 Transmitter power supply interlock circuit.

Fig. 2.3-5 Receiver chain block diagram

- at a duty cycle of 0.2%, and will limit with a maximum cw leakage of 30 mw and maximum spike leakage of 100 mw.

- b) A preselector filter. This filter is centered at 1090 MHz, has a bandwidth of 20 MHz, and provides 40-dB rejection to unwanted signals at the transmitter frequency (1030 MHz.)

- c) A preamplifier. This 1090-MHz solid state amplifier has a noise figure of 2.5 dB, a power gain of 27 dB, and dynamic range of approximately 86 dB. Its 1-dB compression point occurs at an input level of + 12 dBm.

- d) An image filter. This filter has a bandwidth of 120 MHz and an insertion loss of 0.6 dB. Its primary purpose is to reject image frequencies.

- e) A down-converter. The insertion loss of the down-converter is 6 dB when + 7-dBm local oscillator power is injected to the L-port. The unit can withstand up to 400 mw at room temperature (50 mw at 100°C). The 1-dB compression point occurs when the signal power level at the L-port is 1 mw.

- f) An IF amplifier. This amplifier provides 15-dB of gain. Its noise figure is 5 dB, which contributes an insignificant amount of noise to the system's front-end noise power level.

- g) A 60-MHz IF filter. This filter has a signal bandwidth of 10 MHz and establishes the receiver bandwidth. It is a 5-pole Bessel filter adjusted to maintain phase for all frequencies within its 3-dB bandwidth. Its insertion loss is 2 dB. A 6-pole filter was used prior to the interference tests [Ref. 9] and may still be in some units.

- h) A log amplifier. The 60-MHz signal is further amplified and video-detected using a miniature log amplifier. Its center frequency is 60 MHz and bandwidth is 20 MHz; rise-time is 50 nsec. Over an input range of -70 to 0 dBm its output rises from 0.2 to 2 volts into 93 ohms. This represents a transfer characteristic of 25.7 mv/dB. The detected output video is fed to the receiver video monitor and the video pulse quantizer (VPQ).

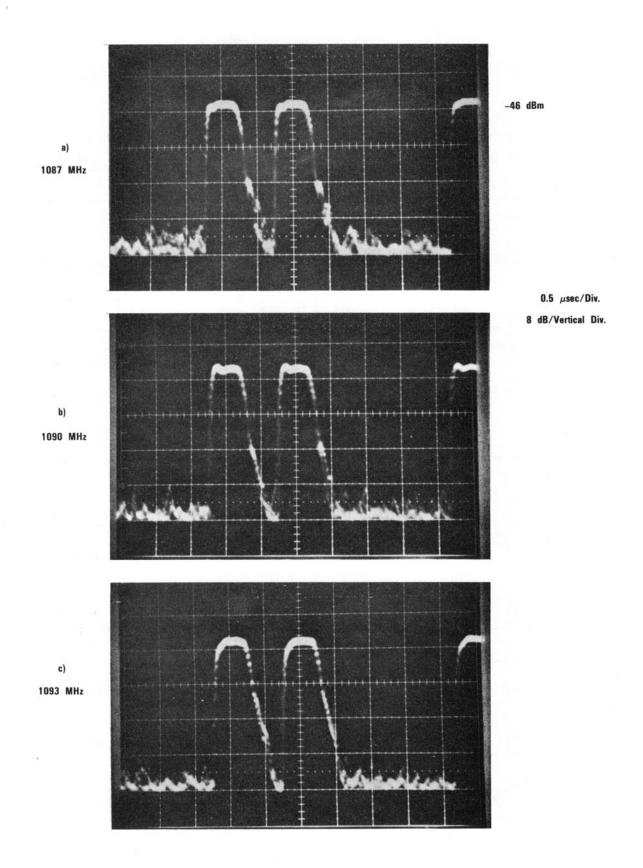

Design of the receiver is based on the power budget and assumptions given in Table 2.3-1. (For more information on TCAS air-to-air power budgets see Ref. 11). Receiver video performance is demonstrated in Fig. 2.3-6a,b,c. This figure indicates a typical receiver log video response for the first two pulses of a Mode S reply preamble at -46 dBm.

#### 2.4 Video Pulse Quantizer

The Video Pulse Quantizer (VPQ) processes receiver log video pulses to produce quantized slope and signal strength, and a Mode S chip amplitude comparison signal. The VPQ is designed to produce, in conjunction with the pulse digitizer described in Section 2.5.2, accurate time-of-arrival and pulse width estimates of all received pulses over the full dynamic range of the receiver, where pulse width and time-of-arrival are defined at the -6 dB points.

32

TABLE 2.3-1

AIR-TO-AIR LINK POWER CALCULATION UNDER NOMINAL CONDITIONS AND AT A RANGE OF 10 NMI.

| ITEM                         | UNITS | INTERROGATION<br>LINK (1030 MHZ) | REPLY<br>LINK (1090 MHZ) |

|------------------------------|-------|----------------------------------|--------------------------|

| l. Transmitter Power         | d Bm  | 57                               | 57                       |

| 2. Transmitter Cabling Loss  | dB    | 3                                | 3                        |

| 3. Transmitter Mismatch Loss | dB    | 0                                | 0                        |

| 4. Transmitter Antenna Gain  | dB    | 0                                | 0                        |

| 5. Free Space Path Loss      | dВ    | 118                              | 118.5                    |

| 6. Receiving Antenna Gain    | dB    | 0                                | 0                        |

| 7. Receiving Mismatch Loss   | dB    | 0                                | 0                        |

| 8. Receiving Cabling Loss    | dB    | 3                                | 3                        |

| 9. Received Power            | d Bm  | -67                              | -67.5                    |

| 10. MTL                      | dBm   | -77                              | -77                      |

| ll. Nominal Margin (One Way) | dB    | 10                               | 9.5                      |

| 12. Nominal Margin (Two Way) | dB    | 9.5                              |                          |

#### Notes:

Items 3 and 7, mismatch losses, refer to the differences, if any, that result when cables are attached to the antennas as compared with connections to perfectly matched loads. The nominal value is arbitrarily taken to be 0 dB.

Items 4 and 6 - the nominal value of aircraft antenna gain is arbitrarily taken to be 0 dB.

Item 5, free space path loss = 20 log(4m  $R/\lambda$ ) where R = range and  $\lambda$  = wavelength.

Item 9, received power equals the sum of items 1, 4 and 6 minus the sum of items 2, 3, 5, 7, and 8.

Item 10, MTL, denotes Minimum Triggering Level.

Item 11, nominal margin (one way) equals item 9 minus item 10. The small difference originates in free space path loss which is slightly different at the two frequencies.

Item 12, nominal margin (two way) is the lesser of the two values in item 11.

Fig. 2.3-6 Receiver log video response.

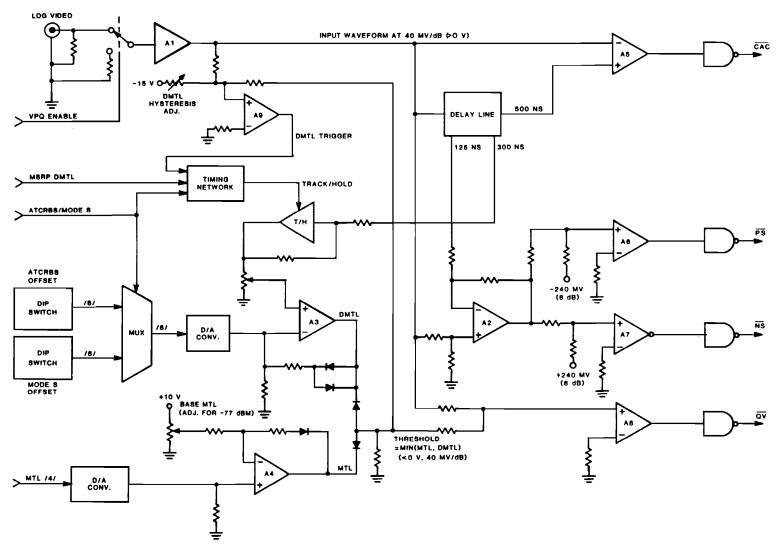

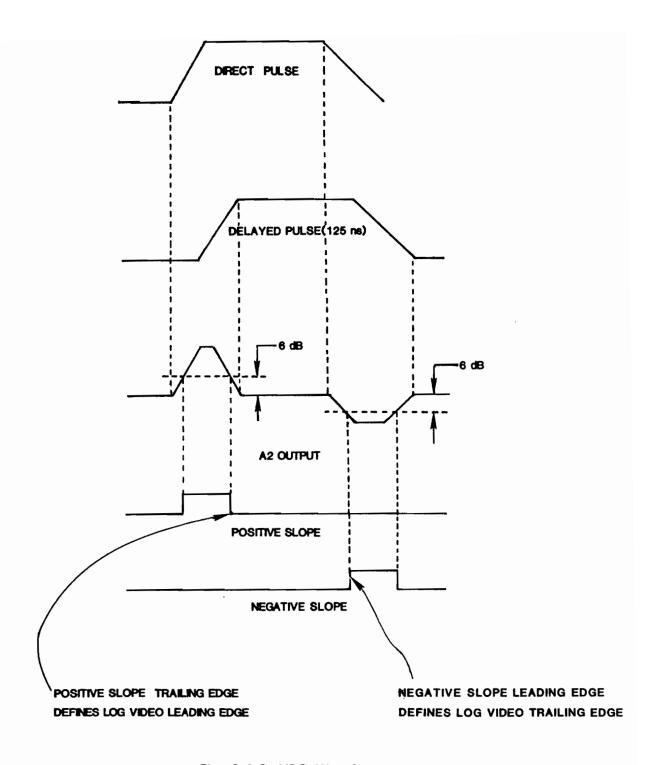

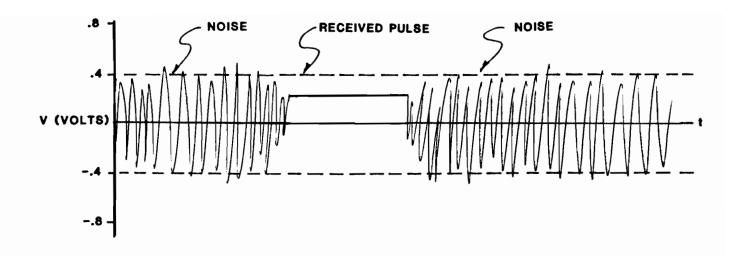

A simplified block diagram of the VPQ is shown in Fig. 2.4-1. Received log video pulses are amplified by Al to produce a 40 mv/dB sensitivity at the Al output. Slope detection is realized by subtracting a delayed version of the reply pulse (125-ns delay) from an undelayed version. As shown in Fig. 2.4-2, slope thresholds may be defined (48 dB per  $\mu\,\text{sec}$ ) such that the outputs from comparators A6 and A7 contain edges which have fixed time relationships with the leading and trailing log video 6-dB points, independent of signal amplitude.

The log video signal strength is quantized by A8 by comparing the output of Al against a threshold level. The threshold is determined by either the fixed minimum threshold level (MTL) or the dynamic minimum threshold level (DMTL) circuitry. These are both negative voltages, and the most negative is selected by the analog OR (implemented with diodes) as the threshold.

The MTL level is determined by a minimum MTL adjustment and a software controlled MTL setting. The minimum MTL is established to give 90% probability of successfully detecting ATCRBS bracket pairs at an input level of -77 dBm at the TEU receiver input port. It is adjusted by the potentiometer at the input to A4. The software may increase the MTL above this level (reduce the sensitivity) in 2-dB (80-mv) steps via the MTL control bits in the MCU control block. These control a D-to-A converter to bias the MTL voltage.

Dynamic MTL is provided to reduce the effect of multipath and low level fruit replies. It does this by raising the threshold level during a reply so that reply pulses will still be above the threshold but multipath due to that reply will normally be below the threshold. Of course, it is possible for multipath to be nearly as strong as the direct signal under some circumstances. DMTL cannot protect against such strong reflections.

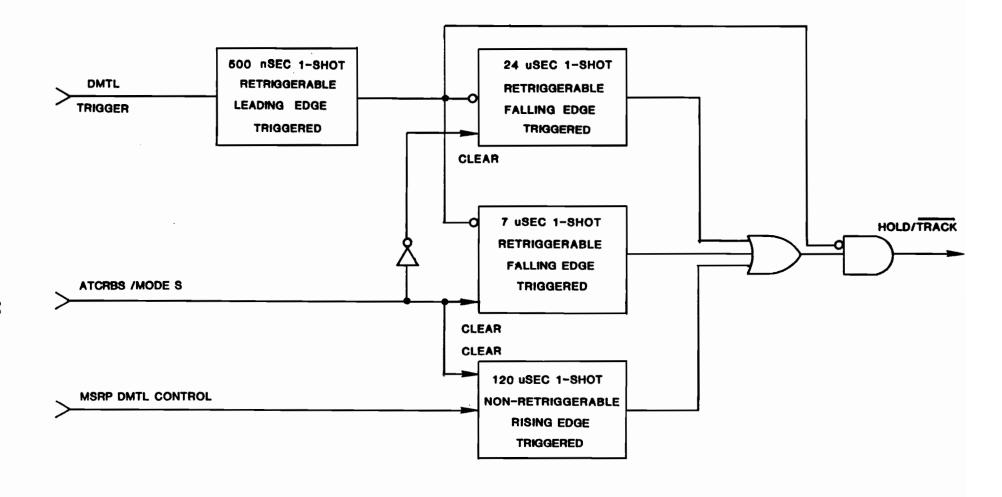

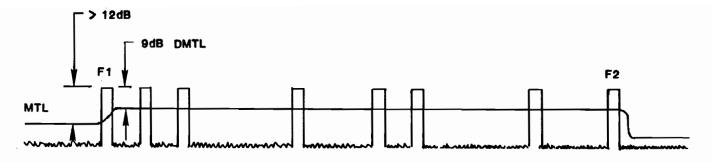

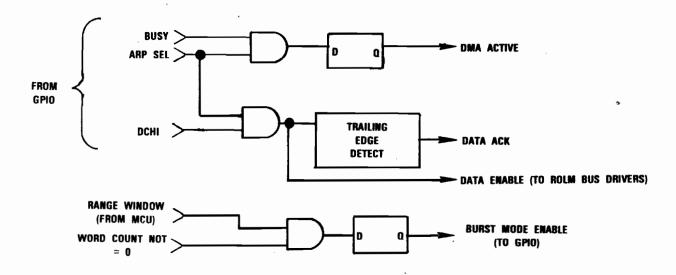

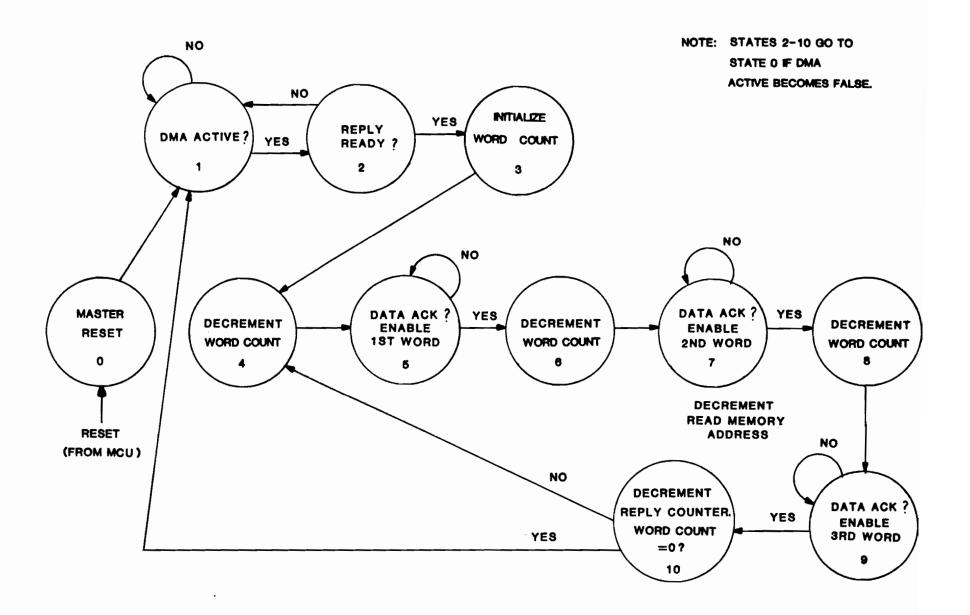

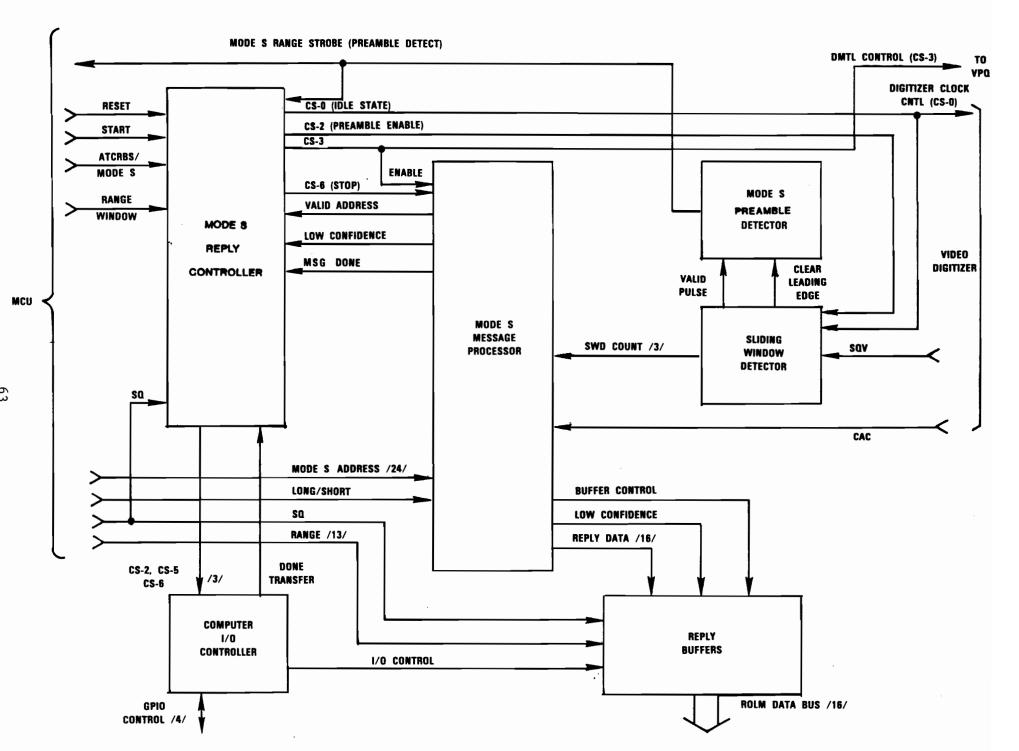

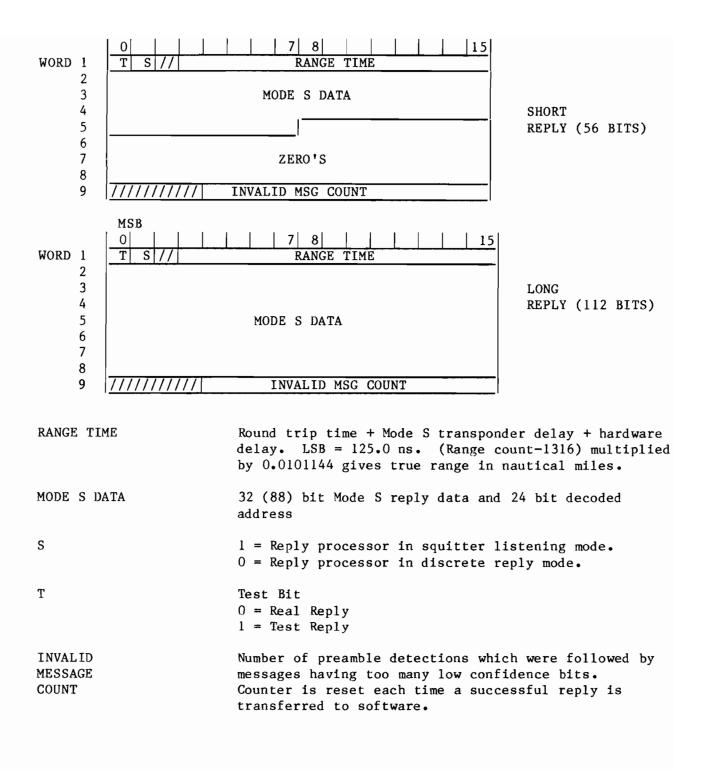

DMTL is activated when the output of Al exceeds the current quantized video threshold by 12 dB (480 mv). This is adjusted by means of the potentiometer at the input to A9. This triggers a timing network, Fig. 2.4-3. The track-and-hold module is forced into track mode (it may or may not have been holding a previous sample). 500 nsec afterward, it is set to hold mode. Since the input to the track-and-hold is delayed by 300 nsec, the signal level held is that 200 nsec following the point that triggered the DMTL.